|

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┤ą╗čÅ ąĖąĘą▓ą╗ąĄą║ą░ąĄą╝čŗčģ ąĮąŠčüąĖč鹥ą╗ąĄą╣ ą┤ą░ąĮąĮčŗčģ (removable storage interface, RSI) čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąĖąĮč鹥čĆč乥ą╣čü čģąŠčüčéą░ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ąĮąĄą╝čā ą║ą░čĆčé MMC (multimedia card), ą║ą░čĆčé ą┐ą░ą╝čÅčéąĖ SD (secure digital) ąĖ ą║ą░čĆčé SDIO (secure digital input/output). ąÆąŠčé čüą┐ąĖčüąŠą║ ąŠčüąĮąŠą▓ąĮčŗčģ ąŠčüąŠą▒ąĄąĮąĮąŠčüč鹥ą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ RSI.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą║ą░čĆčéčŗ MMC (ąĖąĘą▓ą╗ąĄą║ą░ąĄą╝ą░čÅ ąĖą╗ąĖ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ), SD ąĖą╗ąĖ SDIO čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░ą╝ąĖ čłąĖąĮčŗ.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ 1-ą▒ąĖčéąĮčŗą╣ ąĖ 4-ą▒ąĖčéąĮčŗą╣ čĆąĄąČąĖą╝čŗ SD (čĆąĄąČąĖą╝ SPI ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ 1-ą▒ąĖčéąĮčŗą╣, 4-ą▒ąĖčéąĮčŗą╣ ąĖ 8-ą▒ąĖčéąĮčŗą╣ čĆąĄąČąĖą╝čŗ MMC (čĆąĄąČąĖą╝ SPI ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ čāčüčéčĆąŠą╣čüčéą▓ eMMC 4.3 embedded NAND flash.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ą║ą░čĆčé SDHC (ą║ą░čĆčéčŗ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ čüą▓čŗčłąĄ 4 ą│ąĖą│ą░ą▒ą░ą╣čé), čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮą░čÅ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ.

ŌĆó ąÆąĮąĄčłąĮąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ąĖąĘ 10 čüąĖą│ąĮą░ą╗ąŠą▓, ą│ą┤ąĄ ąĖą╝ąĄčÄčéčüčÅ ą╗ąĖąĮąĖąĖ čéą░ą║č鹊ą▓, ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ą┤ąŠ 8 čĆą░ąĘčĆčÅą┤ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ čćą░čüč鹊čéą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ ą║ą░čĆčéčŗ ąĖąĘ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ SCLK.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ SDIO ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ ąĖ ąŠąČąĖą┤ą░ąĮąĖąĄą╝ ąĮą░ čćč鹥ąĮąĖąĖ.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ 32-ą▒ąĖčéąĮąŠą│ąŠ DMA.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ą╗ąĖčćąĖčÅ ą║ą░čĆčéčŗ.

ŌĆó 512-ą▒ąĖčéąĮčŗą╣ FIFO ąĮą░ ą┐ąĄčĆąĄą┤ą░č湥 ąĖ ą┐čĆąĖąĄą╝ąĄ.

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (SYS_BMODE 010, RSI0 Master).

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ RSI ąĖą╝ąĄčÄčéčüčÅ ąĮąĄ ą▓ąŠ ą▓čüąĄčģ ą╝ąŠą┤ąĄą╗čÅčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą╗ąĖąĮąĄą╣ą║ąĖ Blackfin, ąŠąĮąĖ ąĄčüčéčī č鹊ą╗čīą║ąŠ ą▓ ...

ąóą░ą▒ą╗ąĖčåą░ 24-1. ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ RSI.

| ążčāąĮą║čåąĖčÅ |

ąØą░ą╗ąĖčćąĖąĄ |

| ą¤čĆąŠč鹊ą║ąŠą╗ |

| Master |

ąöą░ |

| Slave |

ąØąĄčé |

| ąĪąĖą╝ą┐ą╗ąĄą║čüąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ |

ąöą░ |

| ą¤ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ |

ąöą░ |

| ą¤ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ |

ąØąĄčé |

| ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░ |

| ąæčāč乥čĆ ą┤ą░ąĮąĮčŗčģ |

ąöą░ |

| ąöąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ |

ąöą░ |

| ąöąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝ č湥čĆąĄąĘ DMA |

ąöą░ |

| ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą║ą░ąĮą░ą╗ąŠą▓ DMA |

1 |

| ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ DMA |

ąöą░ |

| ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ |

ąöą░ |

| ąøąŠą║ą░ą╗čīąĮą░čÅ ą┐ą░ą╝čÅčéčī |

ąØąĄčé |

| ąĀą░ą▒ąŠčéą░ čéą░ą║č鹊ą▓ |

SCLK/2 |

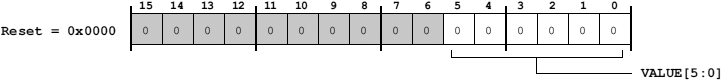

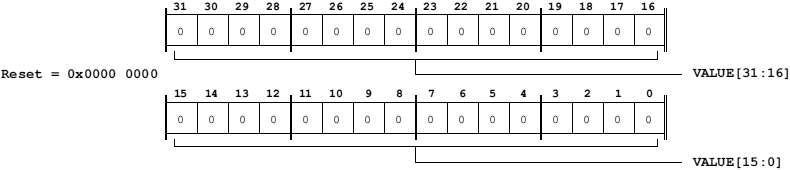

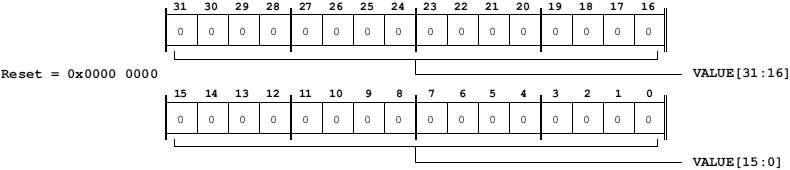

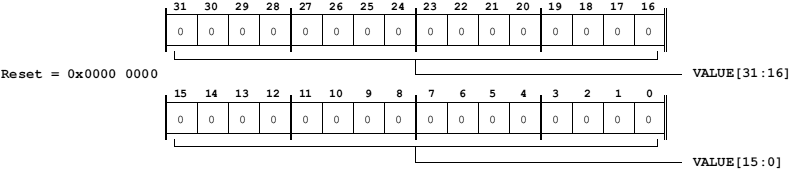

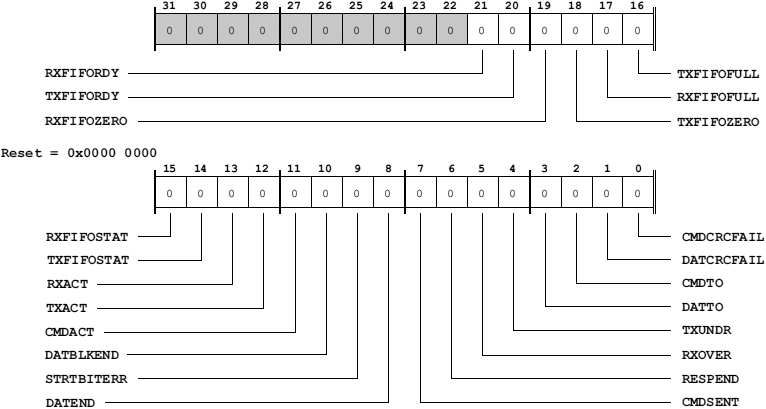

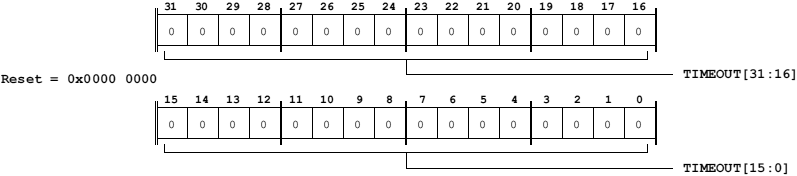

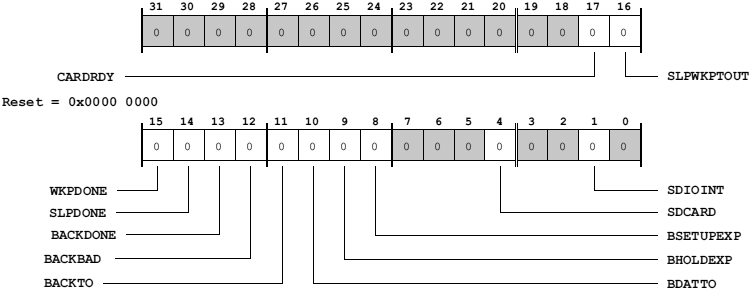

ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖą╣ čü ą║ą░čĆčéą░ą╝ąĖ čüčāčēąĄčüčéą▓čāąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ RSI. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čĆąĄą│ąĖčüčéčĆčā čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▓čĆąĄąĘą║ą░čģ ąĮąĖąČąĄ. ą×ą▒čēą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠ čĆąĄą│ąĖčüčéčĆą░čģ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ 24-17.

ąóą░ą▒ą╗ąĖčåą░ 24-3: ąĪą┐ąĖčüąŠą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ RSI ADSP-BF60x.

| ą×ą┐ąĖčüą░ąĮąĖąĄ |

Trigger ID |

ąóąĖą┐ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ |

| ąÜą░ąĮą░ą╗ DMA RSI0 |

30 |

PULSE/LEVEL (čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā/čāčĆąŠą▓ąĮčÄ) |

ąóą░ą▒ą╗ąĖčåą░ 24-4: ADSP-BF60x RSI Trigger List Trigger Masters.

| ą×ą┐ąĖčüą░ąĮąĖąĄ |

Trigger ID |

ąóąĖą┐ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ |

| ąÜą░ąĮą░ą╗ DMA RSI0 |

30 |

PULSE/LEVEL (čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā/čāčĆąŠą▓ąĮčÄ) |

ąóą░ą▒ą╗ąĖčåą░ 24-5: ADSP-BF60x RSI Trigger List Trigger Slaves.

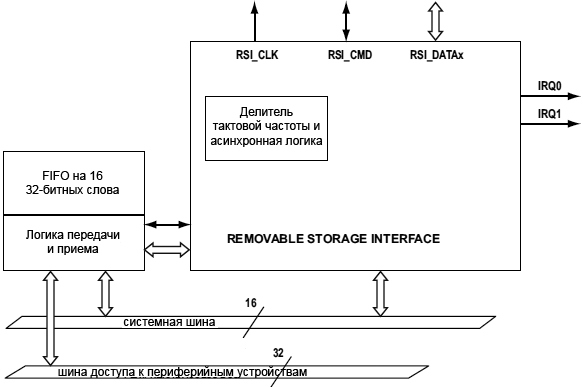

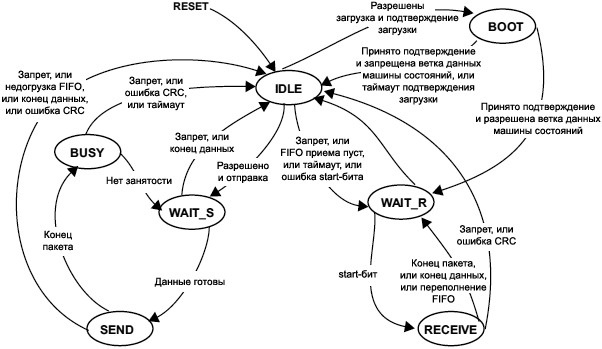

ąĀąĖčüčāąĮąŠą║ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ą▒ą╗ąŠą║ąĖ RSI.

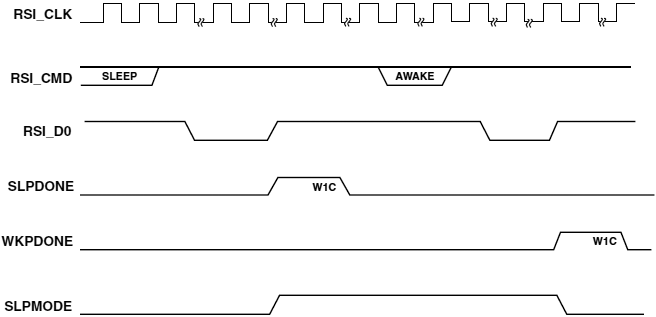

ąĀąĖčü. 24-1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ RSI.

[ąÉčĆčģąĖč鹥ą║čéčāčĆąĮčŗąĄ ą║ąŠąĮčåąĄą┐čåąĖąĖ RSI]

ąÆ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ RSI ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ ąĖą╝ ą┐čĆąŠč鹊ą║ąŠą╗čŗ MMC, SD, SDIO. ą¤ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ ąĖ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖ čüą╗ąĄą┤čāčÄčēąĖą╝ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅą╝ čüčéą░ąĮą┤ą░čĆčéą░ ąĮą░ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ:

ŌĆó MMCA System Specification

ŌĆó JESD84 series of JEDEC standards

ŌĆó SD Specifications Part 1 Physical Layer Specification

ŌĆó SD Specifications Part 1 Physical Layer Simplified Specification

ŌĆó SD Specifications Part E1 SDIO Specification

ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą╝ąĄąČą┤čā ą│ą╗ą░ą▓ąĮąŠą╣ (master, ąĖą╗ąĖ čģąŠčüčé) ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╣ (slave) ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅą╝ąĖ, ą│ą┤ąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ą▓čŗčüčéčāą┐ą░ąĄčé ą║ą░ą║ master, ąĖ ą║ą░čĆčéą░ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ slave. RSI ąŠą▒ą╝ąĄąĮąĖą▓ą░ąĄčéčüčÅ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą┐ąŠ ą┐čĆąŠč鹊ą║ąŠą╗čā čłąĖąĮčŗ, ąŠčüąĮąŠą▓ą░ąĮąĮąŠą╝ ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅčģ, ą║ąŠą│ą┤ą░ čģąŠčüčé ą┐ąŠčüčŗą╗ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą║ąŠą╝ą░ąĮą┤čŗ čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖą│ąĮą░ą╗ą░ RSI_CMD. ąØąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ čéčĆąĄą▒čāčÄčé, čćč鹊ą▒čŗ ą║ą░čĆčéą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖą╗ą░ ą▓ ąŠčéą▓ąĄčé ą┤ą╗čÅ čģąŠčüčéą░ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąŁč鹊čé ąŠčéą▓ąĄčé čéą░ą║ąČąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_CMD.

ą¤ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ą▓ ą║ą░čĆčéčā, čéą░ą║ ąĖ ąĖąĘ ą║ą░čĆčéčŗ, ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą╗ąĖąĮąĖą╣ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą▓ 1, 4 ąĖą╗ąĖ 8, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąĮąŠąČąĄą║ RSI_D0, RSI_D3..RSI_D0 ąĖą╗ąĖ RSI_D7..RSI_D0 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąÆčüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ č湥čĆąĄąĘ ąĮąŠąČą║čā RSI_CMD ąĖ ąĮąŠąČą║ąĖ RSI_D7..RSI_D0 čüąĖąĮčģčĆąŠąĮąĮčŗ čü čüąĖą│ąĮą░ą╗ąŠą╝ ąĮą░ ąĮąŠąČą║ąĄ RSI_CLK.

ąÜąŠą┤čŗ čåąĖą║ą╗ąĖč湥čüą║ąŠą╣ ą┐čĆąŠą▓ąĄčĆą║ąĖ (Cyclic redundancy codes, CRC, ąĖą╗ąĖ ą║ą░ą║ ąŠą▒čŗčćąĮąŠ ąĮą░ąĘčŗą▓ą░čÄčé čŹčéąĖ ą║ąŠą┤čŗ - ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ ąŠčé ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čć ą║ąŠą╝ą░ąĮą┤, ąŠčéą▓ąĄč鹊ą▓ ąĮą░ ą║ąŠą╝ą░ąĮą┤čā ąĖ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą┤ CRC7 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą╣ čģąŠčüč鹊ą╝ ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ą┤ą╗čÅ ą┐ąŠčćčéąĖ ą║ą░ąČą┤ąŠą│ąŠ ąŠčéą▓ąĄčéą░, ą▓ąŠąĘą▓čĆą░čēą░ąĄą╝ąŠą│ąŠ ą║ą░čĆč鹊ą╣ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_CMD. ąÜąŠą┤ CRC16 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ RSI_D7..RSI_D0, čćč鹊ą▒čŗ ąĘą░čēąĖčéąĖčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ. ąÆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ čłąĖąĮčŗ 4 ąĖ 8 ą▒ąĖčé CRC16 ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ.

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓. RSI čŹč鹊 10-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą▓ ą║ąŠč鹊čĆąŠą╝ 1 ą▓čŗą▓ąŠą┤ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, 1 ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤ ąĖ 8 ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ. ąóą░ą▒ą╗ąĖčåą░ 24-6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčüąĮąŠą▓ąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆą░ąĘą╗ąĖčćąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ RSI.

ąóą░ą▒ą╗ąĖčåą░ 24-6. ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ RSI.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ |

| RSI_CLK |

ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ ą║ą░čĆčéčā ąŠčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ RSI. ąÆčüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ čüąĖąĮčģčĆąŠąĮąĮčŗ čü čŹčéąĖą╝ąĖ čéą░ą║čéą░ą╝ąĖ. ą¦ą░čüč鹊čéą░ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ ąŠčé ąĮčāą╗čÅ ą┤ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠč湥ą╣ čćą░čüč鹊čéčŗ, ą║ąŠč鹊čĆčāčÄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ ą║ą░čĆčéą░. ąĪą╝. čéą░ą║ąČąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┤ą░čéą░čłąĖčé ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ. |

| RSI_CMD |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čć ą║ąŠą╝ą░ąĮą┤ ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą║ą░čĆčéčŗ. RSI ąĖčüą┐ąŠą╗čīąĘčāąĄčé čŹč鹊čé čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤ ą▓ ą║ą░čĆčéčā, ąĖ ą║ą░čĆčéą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čŹč鹊čé ąČąĄ čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą▒čĆą░čéąĮąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā RSI ąŠčéą▓ąĄč鹊ą▓ ąĮą░ ą║ąŠą╝ą░ąĮą┤čŗ. ąÆčŗčģąŠą┤ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ RSI ą┤ą╗čÅ čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ (push-pull), ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ (open-drain). ąĀąĄąČąĖą╝ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ą║ą░čĆčéą░ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą▒čēąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ ąĖ ą║ąŠą╝ą░ąĮą┤čŗ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čüąĄ RSI (ą║ą░čĆčéčŗ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą┤čĆčāą│ ą┤čĆčāą│čā), ąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą▓čüąĄčģ ą║ą░čĆčé(1). |

| RSI_D7..RSI_D0 |

ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą▓čüąĄčģ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ą▓ ą║ą░čĆčéčā, čéą░ą║ ąĖ ąĖąĘ ąĮąĄčæ. ą©ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ 1-čĆą░ąĘčĆčÅą┤ąĮą░čÅ, 4-čĆą░ąĘčĆčÅą┤ąĮą░čÅ ąĖ 8-čĆą░ąĘčĆčÅą┤ąĮą░čÅ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čģąŠčéčÅ čĆą░ąĮąĮąĖąĄ čĆąĄą▓ąĖąĘąĖąĖ čüčéą░ąĮą┤ą░čĆčéą░ MMC ą┐ąŠąĘą▓ąŠą╗čÅą╗ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ą░čĆčé MMC ą║ ąŠą┤ąĮąŠą╝čā ąĖąĮč鹥čĆč乥ą╣čüčā RSI, čüčéčĆąŠą│ąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą║ ąŠą┤ąĮąŠą╝čā ąĖą╝ąĄčÄčēąĄą╝čāčüčÅ ąĖąĮč鹥čĆč乥ą╣čüčā čģąŠčüčéą░ RSI. ąŁč鹊ą╣ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĄą╣ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĮąĄ ą▒čāą┤čāčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░čéčīčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĖčģ ąŠą▒čēčāčÄ čłąĖąĮčā ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ąóą░ą▒ą╗ąĖčåą░ 24-7 ąŠą┐ąĖčüčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░ MMC, ąĖ čéą░ą▒ą╗ąĖčåą░ 24-8 ąŠą┐ąĖčüčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ SD ąĖ SDIO.

ąóą░ą▒ą╗ąĖčåą░ 24-7. ą×ą┐ąĖčüą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ RSI MMC.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

1 ą▒ąĖčé |

2 ą▒ąĖčéą░ |

8 ą▒ąĖčé |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ |

| RSI_D7 |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

Data7 |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ |

| RSI_D6 |

Data6 |

| RSI_D5 |

Data5 |

| RSI_D4 |

Data4 |

| RSI_D3 |

Data3 |

Data3 |

| RSI_D2 |

Data2 |

Data2 |

| RSI_D1 |

Data1 |

Data1 |

| RSI_D0 |

Data0 |

Data0 |

Data0 |

| RSI_CMD |

Command/Response |

| RSI_CLK |

ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ |

ąÆčŗčģąŠą┤ |

ąóą░ą▒ą╗ąĖčåą░ 24-8. ą×ą┐ąĖčüą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ RSI SD ąĖ SDIO.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

SD 1 ą▒ąĖčé |

SD 2 ą▒ąĖčéą░ |

SDIO 1 ą▒ąĖčé |

SDIO 2 ą▒ąĖčéą░ |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ |

| RSI_D7 |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ |

| RSI_D6 |

| RSI_D5 |

| RSI_D4 |

| RSI_D3 |

ąøąĖą▒ąŠ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą╗ąĖą▒ąŠ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ |

Data3/ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ą░čĆčéčŗ |

ąøąĖą▒ąŠ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą╗ąĖą▒ąŠ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ |

Data3/ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ą░čĆčéčŗ |

| RSI_D2 |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

Data2 |

Read Wait |

Data2/Read Wait |

| RSI_D1 |

Data1 |

Interrupt |

Data1/Interrupt |

| RSI_D0 |

Data0 |

Data0 |

Data0 |

Data0 |

| RSI_CMD |

Command/Response |

Command/Response/

CCS/CCSD |

| RSI_CLK |

ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ |

ąÆčŗčģąŠą┤ |

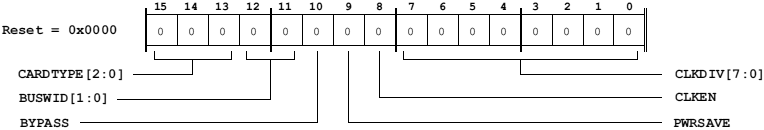

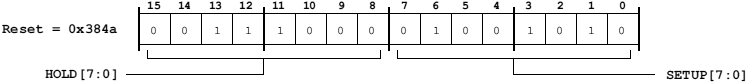

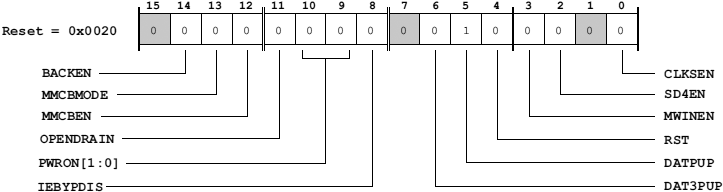

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. RSI čŹč鹊 ą▒čŗčüčéčĆąŠąĄ, čüąĖąĮčģčĆąŠąĮąĮąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ čćą░čüč鹊č鹊ą╣ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆą░čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_CLK. ąśąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā RSI ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ąĖ čłąĖąĮą░ą╝ąĖ čĆą░ą▒ąŠčéą░ąĄčé čü čćą░čüč鹊č鹊ą╣ SCLK (čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin). ą×ą▒ą╝ąĄąĮ ą╝ąĄąČą┤čā ą┤ąŠą╝ąĄąĮąŠą╝ čéą░ą║č鹊ą▓, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ąĮąĄčłąĮąĄ ąŠčé RSI ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_CLK, ąĖ ą┤ąŠčüčéčāą┐ąŠą╝ RSI ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čłąĖąĮą░ą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░č鹊čĆąŠą▓ ą╝ąŠą┤čāą╗čÅ RSI. ą¦ą░čüč鹊čéą░ RSI_CLK ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ 8-ą▒ąĖčéąĮčŗą╝ ą┐ąŠą╗ąĄą╝ RSI_CTL.CLKDIV ąĖ ą▒ąĖč鹊ą╝ RSI_CTL.BYPASS čĆąĄą│ąĖčüčéčĆą░ RSI_CTL.

ąĢčüą╗ąĖ RSI_CTL.BYPASS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ čüąĖą│ąĮą░ą╗ RSI_CLK ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąŠąĮą░ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąŠčé čćą░čüč鹊čéčŗ SCLK. ąĢčüą╗ąĖ RSI_CTL.BYPASS ąŠčćąĖčēąĄąĮ, č鹊 ą╗ąŠą│ąĖą║ą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčā ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čćą░čüč鹊čéčā RSI_CLK ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮąĖąČąĄ, ą│ą┤ąĄ RSI_CTL.CLKDIV čŹč鹊 8-ą▒ąĖčéąĮą░čÅ ą▓ąĄą╗ąĖčćąĖąĮą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0..255.

RSI_CLK = SCLK / 2*(RSI_CTL.CLKDIV+1)

ąÆčŗčģąŠą┤ RSI_CLK čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ RSI_CTL.CLKEN, ąĖ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čäčāąĮą║čåąĖčÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ RSI_CTL.PWRSAVE, čćč鹊 ąĘą░ą┐čĆąĄčēą░ąĄčé ą▓čŗčģąŠą┤ RSI_CLK, ą║ąŠą│ą┤ą░ ąĮąĄčé ą┐ąĄčĆąĄą┤ą░čć č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RSI.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░. RSI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čéąĖą┐ąŠą▓ ą║ą░čĆčé, čĆą░ą▒ąŠčéą░čÄčēąĖčģ čü čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░ą╝ąĖ. ąĀą░ąĘąĮčŗąĄ čéąĖą┐čŗ ą║ą░čĆčé ą╝ąŠą│čāčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮčŗąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░.

ąĪąĖą│ąĮą░ą╗ ą║ąŠą╝ą░ąĮą┤čŗ ąĮą░ ą║ą░čĆčéą░čģ MMC čĆą░ą▒ąŠčéą░ąĄčé ą▓ 2 čĆą░ąĘąĮčŗčģ čĆąĄąČąĖą╝ą░čģ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░ ą║ą░čĆčéčŗ. ąÆ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą║ą░čĆčéčŗ čüąĖą│ąĮą░ą╗ ą║ąŠą╝ą░ąĮą┤čŗ čĆą░ą▒ąŠčéą░ąĄčé ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝. ąÜąŠą│ą┤ą░ ą║ą░čĆčéą░ ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, čŹč鹊čé čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ą┤ą▓čāčģčéą░ą║čéąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▓ąĄčĆčģąĮąĖą╣ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ (pull-up) ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_CMD ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čāą┤ąĄčƹȹ░čéčī čüąĖą│ąĮą░ą╗ ąŠčé ą┐ą╗ą░ą▓ą░ąĮąĖčÅ ą▓ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ pull-up čĆąĄąĘąĖčüč鹊čĆ ąĮąĄ ą┤ąŠčüčéą░č鹊č湥ąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ čäą░ąĘčŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą║ą░čĆčéčŗ, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ MMC-ą║ą░čĆčéčŗ RSI_CMD čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ ąŠčéą║čĆčŗč鹊ą│ąŠ ą║ąŠą╗ą╗ąĄą║č鹊čĆą░. ąĢčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ čāčüčéčĆąŠą╣čüčéą▓ MMC, č鹊 ąĮčāąČąĄąĮ ą▓ąĮąĄčłąĮąĖą╣ pull-up čĆąĄąĘąĖčüč鹊čĆ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ čüąĖą│ąĮą░ą╗čā RSI_CMD čüąŠą│ą╗ą░čüąĮąŠ čüčéą░ąĮą┤ą░čĆčéčā JEDEC.

ąśčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ čłąĖčĆąĖąĮą░ čłąĖąĮčŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ąĮą░ 1, 4 ąĖą╗ąĖ 8 ą▒ąĖčé ą┐ąŠą╗ąĄą╝ RSI_CTL.BUSWID.

ąöą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ ą┐ąŠą╝ąĄčģ ąĖ ą┐ą╗ą░ą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓, ą║ąŠą│ą┤ą░ ą║ą░čĆčéą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą║ą░čĆčéčŗ ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ (ą▓čŗčüąŠą║ąŠąĖą╝ą┐ąĄą┤ą░ąĮčüąĮąŠąĄ) čüąŠčüč鹊čÅąĮąĖąĄ, ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čĆą░ąĘą╗ąĖčćąĮčŗąĄ pull-up ąĖ pull-down ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ RSI_D0..RSI_D7. ąĀąĄą│ąĖčüčéčĆ RSI_CFG ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠą┐čåąĖąĖ.

ŌĆó ąĀą░ąĘčĆąĄčłąĖčéčī ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī pull-up čĆąĄąĘąĖčüč鹊čĆ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_D3.

ŌĆó ąĀą░ąĘčĆąĄčłąĖčéčī ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī pull-up čĆąĄąĘąĖčüč鹊čĆčŗ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ RSI_D7..RSI_D4 ąĖ RSI_D2..RSI_D0.

ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ą░čĆčéčŗ. RSI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī, ą║ąŠą│ą┤ą░ ą║ą░čĆčéą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą▓ ąĄą│ąŠ čüą╗ąŠčé. ąĢčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čüą┐ąŠčüąŠą▒ąŠą▓, ą║ą░ą║ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░ą╗ąĖčćąĖčÅ ą║ą░čĆčéčŗ.

ŌĆó ąśčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 3 čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ. ąÜą░čĆčéčŗ SD ąĖ SDIO ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ pull-up čĆąĄąĘąĖčüč鹊čĆ ąĮą░ ą╗ąĖąĮąĖąĖ RSI_D3 ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī čģąŠčüčéčā, čćč鹊 ą▓ čüą╗ąŠč鹥 ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą║ą░čĆčéą░. ą¦č鹊ą▒čŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī RSI_D3 ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ, ą║ ąĮąĄą╝čā ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮąĄčłąĮąĖą╣ pull-down čĆąĄąĘąĖčüč鹊čĆ (ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą║ GND), čćč鹊ą▒čŗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą▒čŗą╗ ąĮąĖąĘą║ąĖą╣ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī, ą║ąŠą│ą┤ą░ ą║ą░čĆčéą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░.

ąÜąŠą│ą┤ą░ ą║ą░čĆčéą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ čüą╗ąŠčé, ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ RSI_D3 ąĖ RSI_STAT0 ą▒čāą┤ąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ąĮą░čĆą░čüčéą░ąĮąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé SDCARD (ą│ąĄąĮąĄčĆąĖčĆčāčÄčēąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ). ąÜą░ą║ č鹊ą╗čīą║ąŠ ą║ą░čĆčéą░ ą▒čŗą╗ą░ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░ąĮą░, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RSI_STAT0.SDCARD ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠčćąĖčēąĄąĮąŠ ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąŠ. ąóą░ą║ąČąĄ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ pull-up čĆąĄąĘąĖčüč鹊čĆ ą▓ ą║ą░čĆč鹥 SD ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ SET_CLR_CARD_DETECT. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ RSI_D3 ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ čü ą▓ąĮąĄčłąĮąĖą╝ pull-down čĆąĄąĘąĖčüč鹊čĆąŠą╝, ąĮąĄ čĆą░ąĘčĆąĄčłą░ą╣č鹥 ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ pull-up čĆąĄąĘąĖčüč鹊čĆ (ą▒ąĖčé RSI_CFG.DAT3PUP = 0).

ŌĆó ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą║ąŠąĮčéą░ą║č鹊ą▓ čüąŠą║ąĄčéą░ SD/MMC ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą▓čŗą▓ąŠą┤ą░ GPIO. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗą╣ ą╝ąĄč鹊ą┤ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ - ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą╝ąĄčģą░ąĮąĖč湥čüą║ąĖąĄ ą║ąŠąĮčéą░ą║čéčŗ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ ąĮą░ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüąŠą║ąĄč鹊ą▓ ą║ą░čĆčé. ąĪąŠą║ąĄčéčŗ, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖąĄ čŹčéčā ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī, ąĘą░ą╝čŗą║ą░čÄčé ąĮą░ GND čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗, ą║ąŠą│ą┤ą░ ą║ą░čĆčéą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░. ąØą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮąĄčłąĮąĖą╣ pull-up čĆąĄąĘąĖčüč鹊čĆ ą╗čÄą▒ąŠą│ąŠ ą┐ąŠą┤čģąŠą┤čÅčēąĄą│ąŠ ąĮąŠą╝ąĖąĮą░ą╗ą░ (ą┐ąŠčĆčÅą┤ą║ą░ 10..100 ą║ą×ą╝), ąĖ ą┐ąŠą╗čāč湥ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠą┤ą░ąĮ ąĮą░ ą╗čÄą▒čāčÄ ąĮąŠąČą║čā GPIO ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠą│ ą▒čŗ ąŠą┐čĆąŠčüąĖčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĄčæ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖą▒ąŠ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ąŠčé GPIO, ą╗ąĖą▒ąŠ ąŠą┐čĆąŠčüąŠą╝. ąöąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčŗ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą╝ąĄčĆčŗ ą┐ąŠ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÄ ą┤čĆąĄą▒ąĄąĘą│ą░ ą╝ąĄčģą░ąĮąĖč湥čüą║ąĖčģ ą║ąŠąĮčéą░ą║č鹊ą▓ (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗąĄ ąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ).

ąŁč鹊 ąĮą░ąĖą▒ąŠą╗ąĄąĄ ąĮą░ą┤ąĄąČąĮčŗą╣ ąĖ čŹčäč乥ą║čéąĖą▓ąĮčŗą╣ ą╝ąĄč鹊ą┤ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ ąĖąĘą▓ą╗ąĄč湥ąĮąĖčÅ ą║ą░čĆčéčŗ, ą┐ąŠč鹊ą╝čā čćč鹊 čā ąĮąĄą║č鹊čĆčŗčģ ą║ą░čĆčé MMC ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čäčāąĮą║čåąĖčÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ pull-up čĆąĄąĘąĖčüč鹊čĆąŠą╝ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_D3. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą║ą░čĆčéą░ ą▒čŗą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░, ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖąĘą▓ą╗ąĄč湥ąĮąĖąĄ ą║ą░čĆčéčŗ.

ŌĆó ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą┐čĆąŠčüą░ (polling). ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖ ąŠą┐čĆą░čłąĖą▓ą░ąĄčé čüą╗ąŠčé čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą║ąŠą╝ą░ąĮą┤ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą║ą░čĆčéčŗ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗčģ čéąĖą┐ąŠą▓ ą║ą░čĆčé. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą║ą░čĆčéą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░, ą▓ ąŠąĮą░ ąŠčéą▓ąĄčé ąĮą░ ą║ąŠą╝ą░ąĮą┤čā ąŠčéą┐čĆą░ą▓ąĖčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ąŠčéą▓ąĄčé ąŠą▒čĆą░čéąĮąŠ ą║ čģąŠčüčéčā. ąÜąŠą│ą┤ą░ ą║ą░čĆčéą░ ąĖąĘą▓ą╗ąĄč湥ąĮą░, ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čéą░ą╣ą╝ą░čāčé ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ ąŠčéą▓ąĄčéą░ ąĮą░ ą║ąŠą╝ą░ąĮą┤čā (ąŠčéą▓ąĄčé ąĮą░ ą║ąŠą╝ą░ąĮą┤čā ąĮąĄ ą┐čĆąĖą┤ąĄčé).

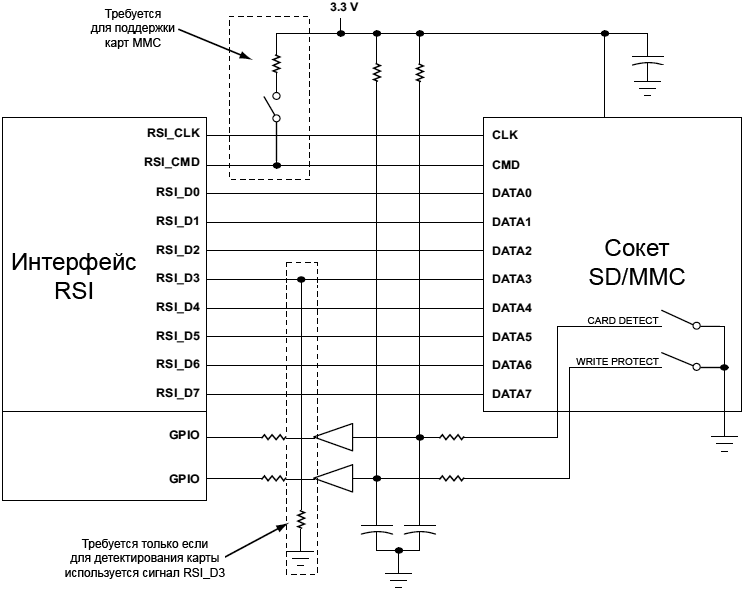

ąØą░ čĆąĖčüčāąĮą║ąĄ 24-2 ą┐ąŠą║ą░ąĘą░ąĮčŗ čāą┐ąŠą╝čÅąĮčāčéčŗąĄ ą▓čŗčłąĄ čüčģąĄą╝čŗ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ.

ąĀąĖčü. 24-2. ąśąĮč鹥čĆč乥ą╣čü čüąŠą║ąĄčéą░ RSI.

RSI čéčĆąĄą▒čāąĄčé 2 ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ čéą░ą║č鹊ą▓, ą║ąŠč鹊čĆčŗąĄ ąĮą░ą┐čĆčÅą╝čāčÄ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąĖąĘ SCLK. ą×ą┤ąĖąĮ ąĖąĘ čŹčéąĖčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ, ąĖ ą┐ąŠčüą╗ąĄ ąĮąĄą│ąŠ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ RSI_CLK.

ą¦č鹊ą▒čŗ RSI ą╝ąŠą│ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░čéčī, čŹčéąĖ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ RSI_CFG.CLKSEN. ą×čćąĖčüčéą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąĘą░ą┐čĆąĄčéąĖčé čĆą░ą▒ąŠčéčā RSI, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ RSI. ąĪąĖą│ąĮą░ą╗ RSI_CLK ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖčéą░ RSI_CTL.CLKEN.

ą£ąŠą│čāčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ąŠą┐čåąĖąĖ ą┤ą╗čÅ čŹą║ąŠąĮąŠą╝ąĖąĖ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ RSI_CTL.PWRSAVE, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┐čĆąĄčéąĖčé ą▓čŗčģąŠą┤ RSI_CLK, ą║ąŠą│ą┤ą░ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RSI ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁčéąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 24-9.

ąóą░ą▒ą╗ąĖčåą░ 24-9. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 菹║ąŠąĮąŠą╝ąĖąĖ 菹ĮąĄčĆą│ąĖąĖ RSI (RSI Power Saving).

| RSI_CFG.CLKSEN |

RSI_CTL.CLKEN |

RSI_CTL.PWRSAVE |

ąĪąŠčüč鹊čÅąĮąĖąĄ RSI |

ąÆčŗčģąŠą┤ RSI_CLK |

| 0 |

0 |

0 |

ąŚą░ą┐čĆąĄčēąĄąĮ |

ąØąĄčé čéą░ą║č鹊ą▓ |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

0 |

ąĀą░ąĘčĆąĄčłąĄąĮ |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

ąØąĄą┐čĆąĄčĆčŗą▓ąĮčŗąĄ čéą░ą║čéčŗ(1) |

| 1 |

1 |

1 |

ąóą░ą║čéčŗ ą┐ąŠą┤ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥(1) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą┐ąŠą╗ąĄ PWRON ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSI_CFG ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0x3. ąĢčüą╗ąĖ PWRON ąŠčćąĖčēąĄąĮ, č鹊 čéą░ą║čéčŗ ąĮąĄ ą▒čāą┤čāčé ą▓čŗą▓ąŠą┤ąĖčéčīčüčÅ.

[ąśąĮč鹥čĆč乥ą╣čü RSI čéąĖą┐ą░ ą║ąŠą╝ą░ąĮą┤ą░ - ąŠčéą▓ąĄčé]

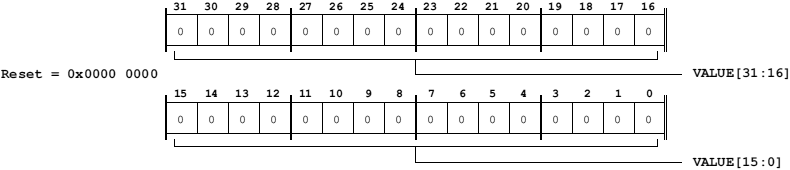

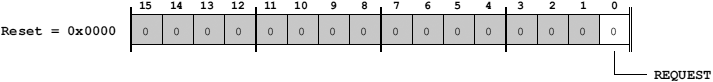

RSI ą┐ąŠčüčŗą╗ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čŗ ą▓ ą║ą░čĆčéčā ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąŠčéą▓ąĄčéčŗ ąŠčé ą║ą░čĆčéčŗ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ RSI_CMD. ąÜąŠą╝ą░ąĮą┤ą░ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ ą║ą░čĆčéčā ą▓čŗą┤ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ čĆąĄą│ąĖčüčéčĆą░ RSI_CMD. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ čüąŠą┤ąĄčƹȹĖčé 6-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ. ą¤ąŠą╗ąĄ IDX čüąŠą┤ąĄčƹȹĖčé ąĖąĮą┤ąĄą║čü ą║ąŠą╝ą░ąĮą┤čŗ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ ą║ą░čĆčéčā. ąśąĮą┤ąĄą║čü ą║ąŠą╝ą░ąĮą┤čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąŠą┤ą┤ąĄčƹȹ║čā ą┤ąŠ 64 ą║ąŠą╝ą░ąĮą┤ - ąŠčé 0 (CMD0) ą┤ąŠ 63 (CMD63).

ąØąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ čéčĆąĄą▒čāčÄčé ą░čĆą│čāą╝ąĄąĮčéą░, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ ą▓ą╝ąĄčüč鹥 čü ą║ąŠą╝ą░ąĮą┤ąŠą╣, čéą░ą║ąĖąĄ ą║ą░ą║ ą░ą┤čĆąĄčü ą┤ą╗čÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čćč鹥ąĮąĖčÅ. ąÉčĆą│čāą╝ąĄąĮčé ą▓čüąĄą│ą┤ą░ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čü ą║ąŠą╝ą░ąĮą┤ąŠą╣, ąĖ ą▓ ąĘąŠąĮąĄ ąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠčüčéąĖ ą║ą░čĆčéčŗ ą▒čāą┤ąĄčé ą╗ąĖą▒ąŠ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī, ą╗ąĖą▒ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąŠą╗ąĄ ą░čĆą│čāą╝ąĄąĮčéą░, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ ą┐čĆąĖąĮčÅč鹊ą╣ ą║ąŠą╝ą░ąĮą┤ąĄ. ąÉčĆą│čāą╝ąĄąĮčé, ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čü ą║ąŠą╝ą░ąĮą┤ąŠą╣, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSI_ARG.

ąÆčüąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ, ąĘą░čēąĖčēąĄąĮąĮčŗąĄ 7-čĆą░ąĘčĆčÅą┤ąĮčŗą╝ ą║ąŠą┤ąŠą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ (cyclic redundancy check, CRC), ą║ąŠč鹊čĆčŗą╣ čćą░čüč鹊 ąĮą░ąĘčŗą▓ą░čÄčé ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝ąŠą╣ CRC7. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī ąĮą░ą╗ąĖčćąĖąĄ ą▓ ą┐ąĄčĆąĄą┤ą░č湥 ąŠčłąĖą▒ąŠą║, ąĖ ą┐ąŠą▓č鹊čĆąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī ą║ąŠą╝ą░ąĮą┤čā, ąĄčüą╗ąĖ ąŠčłąĖą▒ą║ą░ ą┐čĆąŠąĖąĘąŠčłą╗ą░. ąÆčüąĄ ą║ąŠą╝ą░ąĮą┤čŗ, ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ ą▓ ą║ą░čĆčéčā, čüąŠčüčéą░ą▓ą╗ąĄąĮčŗ ąĖąĘ 48 ą▒ąĖčé, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ.

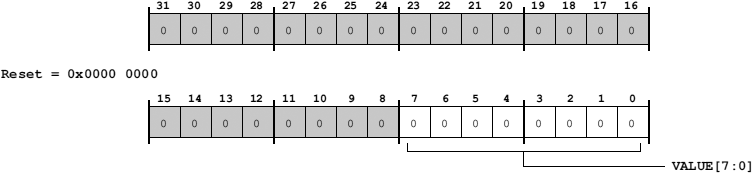

ąóą░ą▒ą╗ąĖčåą░ 24-10. ążąŠčĆą╝ą░čé ą║ąŠą╝ą░ąĮą┤čŗ RSI ą┤ą╗čÅ ą║ą░čĆčéčŗ.

| ą¤ąŠąĘąĖčåąĖčÅ ą▒ąĖčéą░ |

ą©ąĖčĆąĖąĮą░ |

ąŚąĮą░č湥ąĮąĖąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 47 |

1 |

0 |

start-ą▒ąĖčé |

| 46 |

1 |

1 |

ąæąĖčé, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╣, ą║č鹊 ą┐ąĄčĆąĄą┤ą░ąĄčé (transmitter bit) |

| [45:40] |

6 |

x |

ąśąĮą┤ąĄą║čü (ą║ąŠą┤) ą║ąŠą╝ą░ąĮą┤čŗ |

| [39:8] |

32 |

x |

ąÉčĆą│čāą╝ąĄąĮčé ą║ąŠą╝ą░ąĮą┤čŗ |

| [7:1] |

7 |

x |

CRC7 |

| 0 |

1 |

1 |

end-ą▒ąĖčé |

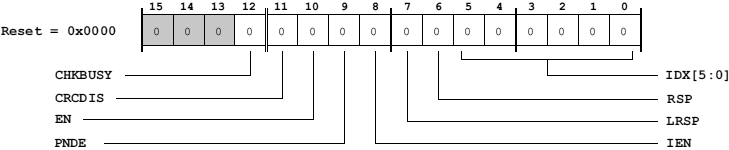

ąĀąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ RSI_CMD čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹊ą╝, ąĮčāąČąĮąŠ ą╗ąĖ ą┤ąŠąČąĖą┤ą░čéčīčüčÅ ąŠčéą▓ąĄčéą░ ąŠčé ą║ą░čĆčéčŗ, ąĖ ąŠ čéąĖą┐ąĄ čŹč鹊ą│ąŠ ąŠčéą▓ąĄčéą░.

RSI ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ RSI_CMD.RSP ąĖ RSI_CMD.LRSP ą┤ą╗čÅ ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠčéą▓ąĄčéą░ ą║ą░čĆčéčŗ (response), čéąĖą┐čŗ ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąĖą╗ąĖ ą┤ą╗ąĖąĮąĮąŠą│ąŠ ąŠčéą▓ąĄčéą░ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čéą░ą▒ą╗ąĖčåą░čģ.

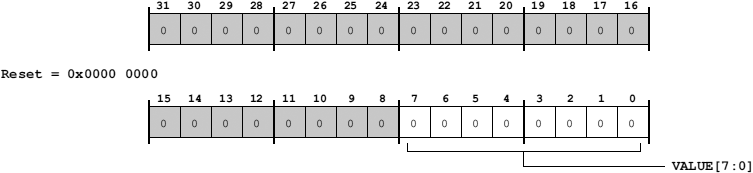

ąóą░ą▒ą╗ąĖčåą░ 24-11. ążąŠčĆą╝ą░čé ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąŠčéą▓ąĄčéą░ ą┤ą╗čÅ RSI RSI Short Response.

| ą¤ąŠąĘąĖčåąĖčÅ ą▒ąĖčéą░ |

ą©ąĖčĆąĖąĮą░ |

ąŚąĮą░č湥ąĮąĖąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 47 |

1 |

0 |

start-ą▒ąĖčé |

| 46 |

1 |

0 |

ąæąĖčé, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╣, ą║č鹊 ą┐ąĄčĆąĄą┤ą░ąĄčé (transmitter bit) |

| [45:40] |

6 |

x |

ąśąĮą┤ąĄą║čü (ą║ąŠą┤) ą║ąŠą╝ą░ąĮą┤čŗ, ąĖą╗ąĖ ą▒ąĖčéčŗ ą┐čĆąŠą▓ąĄčĆą║ąĖ(1) (check bits)

|

| [39:8] |

32 |

x |

ąĪčéą░čéčāčü ą║ą░čĆčéčŗ, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ąĖą╗ąĖ ą┐ąŠą╗ąĄ ą░čĆą│čāą╝ąĄąĮčéą░ |

| [7:1] |

7 |

x |

CRC7 ąĖą╗ąĖ ą▒ąĖčéčŗ ą┐čĆąŠą▓ąĄčĆą║ąĖ(2) |

| 0 |

1 |

1 |

end-ą▒ąĖčé |

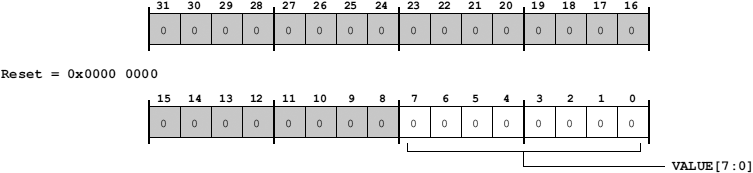

ąóą░ą▒ą╗ąĖčåą░ 24-12. ążąŠčĆą╝ą░čé ą┤ą╗ąĖąĮąĮąŠą│ąŠ ąŠčéą▓ąĄčéą░ ą┤ą╗čÅ RSI (RSI Long Response).

| ą¤ąŠąĘąĖčåąĖčÅ ą▒ąĖčéą░ |

ą©ąĖčĆąĖąĮą░ |

ąŚąĮą░č湥ąĮąĖąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 135 |

1 |

0 |

start-ą▒ąĖčé |

| 134 |

1 |

0 |

ąæąĖčé, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╣, ą║č鹊 ą┐ąĄčĆąĄą┤ą░ąĄčé (transmitter bit) |

| [133:128] |

6 |

111111 |

ąæąĖčéčŗ ą┐čĆąŠą▓ąĄčĆą║ąĖ(1) (check bits)

|

| [127:1] |

127 |

x |

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░, ą▓ą║ą╗čÄčćą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ CRC7(2) |

| 0 |

1 |

1 |

end-ą▒ąĖčé |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåą░ą╝ 24-11 ąĖ 24-12:

(1) ąÆ ąŠčéą▓ąĄčéą░čģ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čüąŠą┤ąĄčƹȹ░čé ąĖąĮą┤ąĄą║čü ą║ąŠą╝ą░ąĮą┤čŗ, ą┐ąŠą╗ąĄ ą▒ąĖčé ą┐čĆąŠą▓ąĄčĆą║ąĖ čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ 111111b.

(2) ąÆ ąŠčéą▓ąĄčéą░čģ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čüąŠą┤ąĄčƹȹ░čé ą║ąŠąĮčéčĆąŠą╗čīąĮčāčÄ čüčāą╝ą╝čā CRC7, ą┐ąŠą╗ąĄ ą▒ąĖčé ą┐čĆąŠą▓ąĄčĆą║ąĖ čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ 111111b.

ąÜą░ą║ ąĖ ą║ąŠą╝ą░ąĮą┤čŗ, ą▓čüąĄ ąŠčéą▓ąĄčéčŗ (response) ą┐ąŠčüčŗą╗ą░čÄčéčüčÅ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_CMD. ąÆ ąŠčéą▓ąĄč鹥 ą▓čüąĄą│ą┤ą░ čüčéą░čĆč鹊ą▓čŗą╣ ą▒ąĖčé čĆą░ą▓ąĄąĮ 0, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ąĖčé ą┐ąĄčĆąĄą┤ą░čćąĖ 0. ąŁčéąĖą╝ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠčé ą║ą░čĆčéčŗ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā RSI. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą║ąŠą╝ą░ąĮą┤, ą║ąŠč鹊čĆčŗąĄ ą▓čŗą┤ą░ąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI, ąĮąĄ ą▓čüąĄ ąŠčéą▓ąĄčéčŗ ąĘą░čēąĖčēąĄąĮčŗ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝ąŠą╣ CRC7. ą×čéąĮąŠčüąĖč鹥ą╗čīąĮąŠ č鹊ą│ąŠ, ąĘą░čēąĖčēąĄąĮ ą╗ąĖ CRC7 ą║ą░ą║ąŠą╣-č鹊 ąŠčéą▓ąĄčé ąĮą░ ą║ąŠą╝ą░ąĮą┤čā, čüą╝. čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÄ [2] ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ č乊čĆą╝ą░čéą░ą╝ ąŠčéą▓ąĄč鹊ą▓ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ą░čĆčéčŗ.

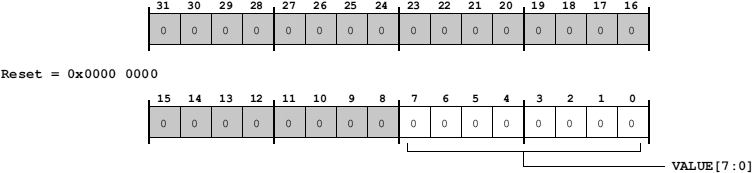

ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé ą║ąŠčĆąŠčéą║ąĖą╣ ąŠčéą▓ąĄčé, ąŠąĮ čĆą░ąĘą▒ąĖą▓ą░ąĄčéčüčÅ ąĮą░ čćą░čüčéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ RSI. 32-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ, čüąŠą┤ąĄčƹȹ░čēąĄąĄ ą▒ąĖčéčŗ [39:8], čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSI_RESP0, ą│ą┤ąĄ ą▒ąĖčé 39 ąŠčéą▓ąĄčéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▒ąĖčéčā 31 čĆąĄą│ąĖčüčéčĆą░ RSI_RESP0, ąĖ ą▒ąĖčé 8 ąŠčéą▓ąĄčéą░ ą▒ąĖčéčā 0 čĆąĄą│ąĖčüčéčĆą░ RSI_RESP0. ąæąĖčéčŗ [45:40] ąŠčéą▓ąĄčéą░ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSI_RESP_CMD.

ąöą╗čÅ ą┤ą╗ąĖąĮąĮąŠą│ąŠ ąŠčéą▓ąĄčéą░ ąĄą│ąŠ ą▒ąĖčéčŗ [127:1] čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ RSI_RESP0, RSI_RESP1, RSI_RESP2 ąĖ RSI_RESP3. ąæąĖčé 31 RSI_RESP0 čüąŠą┤ąĄčƹȹ░čé čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB ą▒ąĖčé 127 ąŠčéą▓ąĄčéą░), ąĖ ą▒ąĖčé 0 RSI_RESP3 cčüąŠą┤ąĄčƹȹĖčé ą▒ąĖčé 1 ąŠčéą▓ąĄčéą░. ąæąĖčé 31 čĆąĄą│ąĖčüčéčĆą░ RSI_RESP3 ą▓čüąĄą│ą┤ą░ čĆą░ą▓ąĄąĮ 0.

ąĪą╗ąĄą┤čāčÄčēąĖą╣ čĆąĖčüčāąĮąŠą║ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čāčéčī ą║ąŠą╝ą░ąĮą┤čŗ ą▓ ą╝ą░čłąĖąĮąĄ čüąŠčüč鹊čÅąĮąĖą╣ RSI. ą¦č鹊ą▒čŗ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ čüčéą░ą╗ą░ ą░ą║čéąĖą▓ąĮąŠą╣, RSI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą▒ąĖč鹊ą╝ RSI_CTL.CLKEN. ąŚą░ą┐čĆąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ RSI ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą▓ąŠąĘą▓čĆą░čéčā ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĄ (IDLE state).

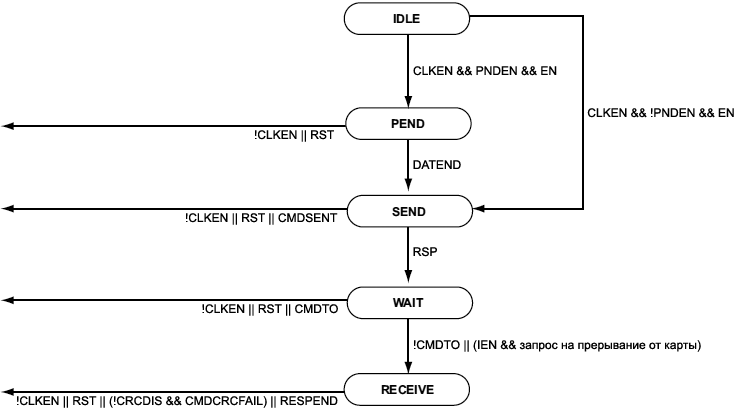

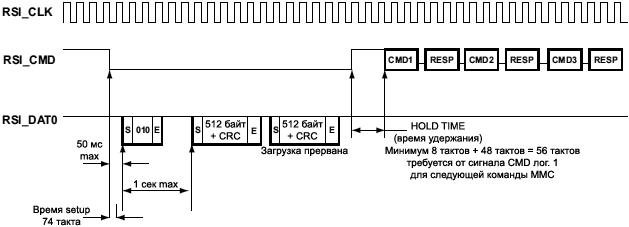

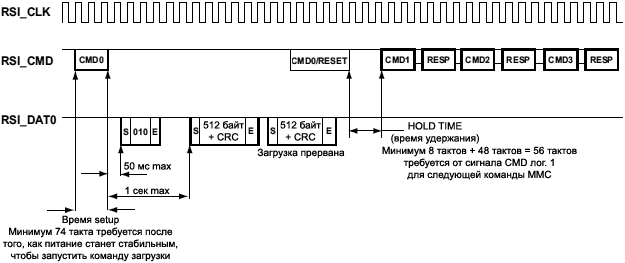

ąĀąĖčü. 24-3. ąÆąĄčéą║ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ąŠą╝ą░ąĮą┤čŗ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ RSI.

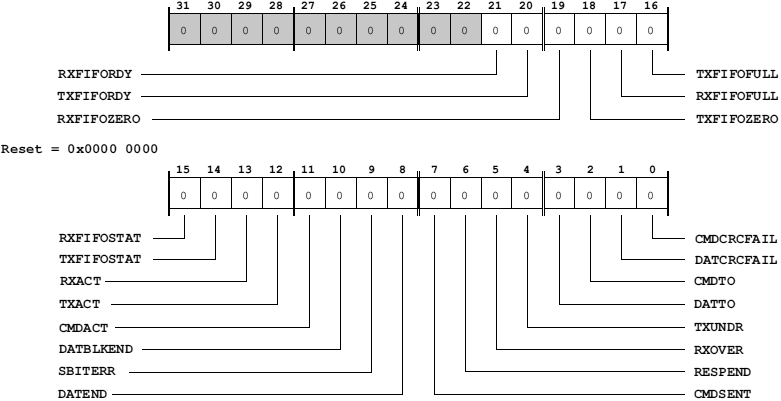

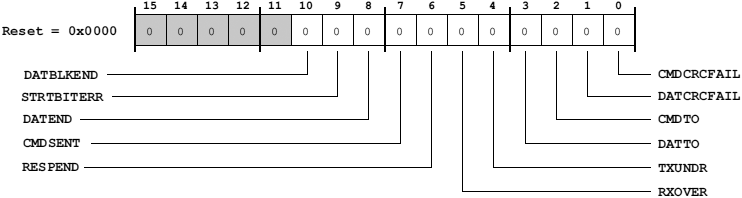

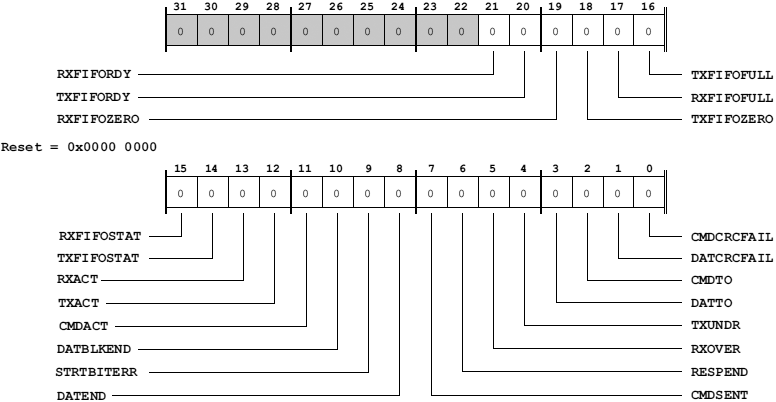

ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ ą▓ ą╝ą░čłąĖąĮąĄ čüąŠčüč鹊čÅąĮąĖą╣ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ čāčüčéą░ąĮąŠą▓ą║čā ąĖ ąŠčćąĖčüčéą║čā ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čäą╗ą░ą│ąŠą▓ čüčéą░čéčāčüą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSI_XFRSTAT. ąĪą╗ąĄą┤čāčÄčēą░čÅ čéą░ą▒ą╗ąĖčåą░ ą┐ąĄčĆąĄčćąĖčüą╗čÅąĄčé čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ (status flags) ąĖ čäą╗ą░ą│ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (exception flags), ąĮą░ ą║ąŠč鹊čĆčŗąĄ ą▓ą╗ąĖčÅąĄčé ą┐čāčéčī ą║ąŠą╝ą░ąĮą┤čŗ ą▓ ą╝ą░čłąĖąĮąĄ čüąŠčüč鹊čÅąĮąĖą╣.

ąóą░ą▒ą╗ąĖčåą░ 24-13. ążą╗ą░ą│ąĖ čüčéą░čéčāčüą░ ą▓ąĄčéą║ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ąŠą╝ą░ąĮą┤ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ RSI.

| ążą╗ą░ą│ RSI_XFRSTAT/RSI_STAT0 |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąĪąŠčüč鹊čÅąĮąĖąĄ, ą▓ ą║ąŠč鹊čĆąŠą╝ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ |

| RSI_XFRSTAT.CMDACT |

ą¤čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░ ą║ąŠą╝ą░ąĮą┤čŗ |

WAIT_S |

| RSI_XFRSTAT.CMDSENT |

ąŻčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░, ą║ąŠč鹊čĆąŠą╣ ąĮąĄ ąĮčāąČąĄąĮ ąŠčéą▓ąĄčé |

SEND |

| RSI_XFRSTAT.CMDTO |

ą¤čĆąŠąĖąĘąŠčłąĄą╗ čéą░ą╣ą╝ą░čāčé ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ ąŠčéą▓ąĄčéą░ ąĮą░ ą║ąŠą╝ą░ąĮą┤čā (ą┐čĆąŠčłą╗ąŠ 64 čéą░ą║čéą░ RSI_CLK) |

WAIT_S |

| RSI_XFRSTAT.CMDCRCFAIL |

ą×čłąĖą▒ą║ą░ CRC ą▓ ąŠčéą▓ąĄč鹥 ąĮą░ ą║ąŠą╝ą░ąĮą┤čā |

RECEIVE |

| RSI_XFRSTAT.RESPEND |

ą×čéą▓ąĄčé ą▒čŗą╗ ą┐čĆąĖąĮčÅčé čāčüą┐ąĄčłąĮąŠ (ąĖ ą┐čĆąŠčłąĄą╗ ą┐čĆąŠą▓ąĄčĆą║čā ąĮą░ CRC, ąĄčüą╗ąĖ ą▒čŗą╗ ąŠčćąĖčēąĄąĮ ą▒ąĖčé CRCDIS) |

RECEIVE |

ą¤čāčéčī ą║ąŠą╝ą░ąĮą┤čŗ čĆą░ą▒ąŠčéą░ąĄčé ą▓ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, čéą░ą║ čćč鹊 ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ąŠčéą▓ąĄčéčŗ ąĮą░ ąĮąĖčģ ąĮąĄ ą╝ąŠą│čāčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąøąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ ą║ą░čĆč鹥, ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąŠčéą▓ąĄčé ąŠčé ą║ą░čĆčéčŗ (ą┐ąŠ-ą┤čĆčāą│ąŠą╝čā ąĖ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤ ąĖ ąŠčéą▓ąĄč鹊ą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮą░čÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ ą╗ąĖąĮąĖčÅ RSI_CMD). ąĢčüą╗ąĖ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ SEND, ą▓čŗčģąŠą┤ RSI_CMD ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ (ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝) čüąŠčüč鹊čÅąĮąĖąĖ čü ą▓čŗčüąŠą║ąĖą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝.

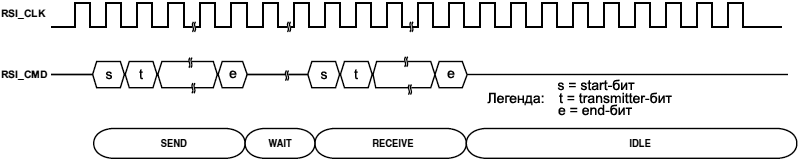

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čéąĖą┐ąĖčćąĮą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ąŠčéą▓ąĄčéą░ ąĮą░ ąĮąĄčæ, čüąĖą│ąĮą░ą╗ RSI_CMD ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░čĆč鹊ą╣ ąĖ čģąŠčüč鹊ą╝ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ RSI_CLK.

ąĀąĖčü. 24-4. ą¤ąĄčĆąĄą┤ą░čćą░ ą║ąŠą╝ą░ąĮą┤čŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ RSI.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ čüąĄą║čåąĖąĖ ąŠą┐ąĖčüčŗą▓ą░čÄčé ą┐čāčéąĖ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ąŠą╝ą░ąĮą┤ RSI.

IDLE State. ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ IDLE, ą║ąŠą│ą┤ą░ ąŠąĮą░ ąĮąĄ ą░ą║čéąĖą▓ąĮą░, ąĖ ą╝ą░čłąĖąĮą░ ą▓čŗą╣ą┤ąĄčé ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ IDLE, ą║ąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RSI_CMD.EN. ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ PEND, ąĄčüą╗ąĖ ą▒ąĖčé RSI_CMD.PNDEN čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖąĮą░č湥 ą▒čāą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ SEND.

ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ IDLE ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 8 čéą░ą║č鹊ą▓ RSI_CLK, ą║ąŠą│ą┤ą░ ą╝ą░čłąĖąĮą░ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE ąĖąĘ ą┤čĆčāą│ąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ, ąĖ ą║ąŠą│ą┤ą░ ą▓ąŠąĘą▓čĆą░čé ą▒čŗą╗ ąĮąĄ ą┐ąŠ ą┐čĆąĖčćąĖąĮąĄ ąĘą░ą┐čĆąĄčéą░ RSI ąĖą╗ąĖ čüą▒čĆąŠčüą░. ąÆ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ 8 čéą░ą║č鹊ą▓ RSI_CLK ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé ą▓čŗą┤ą░ą▓ą░čéčī čüąĖą│ąĮą░ą╗ RSI_CLK, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RSI_CTL.PWRSAVE. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą║ą░čĆč鹥 ąĘą░ą▓ąĄčĆčłąĖčéčī č鹥ą║čāčēčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ. ąÜąŠą│ą┤ą░ ą╝ą░čłąĖąĮą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čüąĮąŠą▓ą░, ąŠąĮą░ ą┐ąŠą║ąĖąĮąĄčé čüąŠčüč鹊čÅąĮąĖąĄ IDLE č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ 8 čéą░ą║č鹊ą▓ RSI_CLK.

PEND State. RSI ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ PEND, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RSI_CMD.PNDEN. ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ PEND, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠą┐ąŠą▓ąĄčēąĄąĮą░ ąŠčé čüčāą▒ą▒ą╗ąŠą║ą░ ą┐čāčéąĖ ą┤ą░ąĮąĮčŗčģ ąŠ č鹊ą╝, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░. ąŁč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čäą╗ą░ą│ą░ RSI_XFRSTAT.DATEND, ą║ąŠą│ą┤ą░ ą┤ąĄą║čĆąĄą╝ąĄąĮčé čüč湥čéčćąĖą║ą░ RSI_DATA_CNT ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą║ąŠą╝ą░ąĮą┤čŗ STOP_TRANSMISSION ą┐ąŠčüą╗ąĄ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ čéčĆąĄą▒čāąĄą╝ąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┤ą░ąĮąĮčŗčģ ą▓ čéčĆą░ąĮąĘą░ą║čåąĖčÅčģ ą┐ąŠč鹊ą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ążčāąĮą║čåąĖčÅ RSI_CMD.PNDEN ąĮąĄą┤ąŠčüčéčāą┐ąĮą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čć, ąŠčüąĮąŠą▓ą░ąĮąĮčŗčģ ąĮą░ ą▒ą╗ąŠą║ą░čģ, ąĖ ąĮąĄ ą╝ąŠąČąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗą┤ą░ą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤čā STOP_TRANSMISSION ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ MULTIPLE_BLOCK_READ ąĖą╗ąĖ MULTIPLE_BLOCK_WRITE (ą╝ąĮąŠą│ąŠą▒ą╗ąŠčćąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ).

SEND State. ąÆąŠ ą▓čĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅ SEND, ą║ąŠąĮčéčĆąŠą╗ąĄčĆ RSI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäą╗ą░ą│ RSI_XFRSTAT.CMDACT čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ ą┐ąŠčüą╗ąĄ ąŠčéą┐čĆą░ą▓ą║ąĖ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ąŠąČąĖą┤ą░ąĄčéčüčÅ ą╗ąĖ ąŠčéą▓ąĄčé ąĮą░ ą║ąŠą╝ą░ąĮą┤čā ąŠčé ą║ą░čĆčéčŗ.

ąĢčüą╗ąĖ ąŠčéą▓ąĄčé ąĮąĄ ąŠąČąĖą┤ą░ąĄčéčüčÅ, č鹊 RSI ąŠčćąĖčēą░ąĄčé čäą╗ą░ą│ RSI_XFRSTAT.CMDACT ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäą╗ą░ą│ RSI_XFRSTAT.CMDSENT, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, čćč鹊 ą▒čŗą╗ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą▒ąĄąĘ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąŠčéą▓ąĄčéą░ ąŠčé ą║ą░čĆčéčŗ. ąŚą░č鹥ą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄčģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ąĢčüą╗ąĖ ąŠčé ą║ą░čĆčéčŗ ąŠąČąĖą┤ą░ąĄčéčüčÅ ąŠčéą▓ąĄčé, č鹊 RSI ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT.

WAIT State. ąÆ čüąŠčüč鹊čÅąĮąĖąĖ WAIT ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ąŠąČąĖą┤ą░ąĄčé ą┐čĆąĖąĄą╝ ąŠčéą▓ąĄčéą░ (response) č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_CMD. ą¤čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čéą░ą╣ą╝ąĄčĆ. ąĢčüą╗ąĖ ąŠčéą▓ąĄčé ąĮąĄ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé ąĘą░ 64 čéą░ą║čéą░ RSI_CLK, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.CMDTO, ąĖ ąŠčćąĖčüčéąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.CMDACT. ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą▓ąŠą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE, ąŠąČąĖą┤ą░čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ.

ąÜąŠą│ą┤ą░ ąŠčéą▓ąĄčé ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ąŠčé ą║ą░čĆčéčŗ, ąŠąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ąĮčāą╗ąĄą╝ ą▓ čüčéą░čĆč鹊ą▓ąŠą╝ ą▒ąĖč鹥 ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_CMD, ąĖ čŹč鹊 ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé RSI ą▓ čüąŠčüč鹊čÅąĮąĖąĄ RECEIVE, ąĖ ą▓ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąĖąĄą╝ 48-ą▒ąĖčéąĮąŠą│ąŠ ąĖą╗ąĖ 136-ą▒ąĖčéąĮąŠą│ąŠ ąŠčéą▓ąĄčéą░ ą║ą░čĆčéčŗ (response).

ąĪąŠčüč鹊čÅąĮąĖąĄ WAIT čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ. ąŁč鹊 ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖčÅ (čĆą░ą▒ąŠčéą░ ą║ąŠč鹊čĆąŠą╣ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ RSI_CMD.IEN), ąŠčéąĮąŠčüčÅčēą░čÅčüčÅ č鹊ą╗čīą║ąŠ ą║ ą║ą░čĆčéą░ą╝ MMC. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čéą░ą╣ą╝ąĄčĆ čéą░ą╣ą╝ą░čāčéą░, ą║ąŠč鹊čĆčŗą╣ ąŠą▒čŗčćąĮąŠ čüčéą░čĆčéčāąĄčé ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT, ąĘą░ą┐čĆąĄčēąĄąĮ. RSI ąŠčüčéą░ąĄčéčüčÅ ą▓ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ą░čĆčéčŗ.

ąÜą░čĆčéčŗ, ą║ąŠč鹊čĆčŗąĄ čĆąĄą░ą╗ąĖąĘčāčÄčé čŹčéčā čäčāąĮą║čåąĖčÄ, ą╝ąŠą│čāčé ąĖą╝ąĄčéčī ąŠčéą╗ąŠąČąĄąĮąĮčŗą╣ ąŠčéą▓ąĄčé, ą║ąŠč鹊čĆčŗą╣ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā čüąŠą▒čŗčéąĖčÄ ą║ą░čĆčéčŗ. ąÜą░ą║ č鹊ą╗čīą║ąŠ čŹč鹊 čüąŠą▒čŗčéąĖąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ, ą║ą░čĆčéą░ ą┐ąŠčüčŗą╗ą░ąĄčé ąŠčéą▓ąĄčé. ąóąŠą│ą┤ą░ RSI ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé start-ą▒ąĖčé ąŠčéą▓ąĄčéą░ ąĖ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ RECEIVE.

RECEIVE State. ąÆ čüąŠčüč鹊čÅąĮąĖąĖ RECEIVE ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI čćąĖčéą░ąĄčé ąŠčéą▓ąĄčé ąŠčé ą║ą░čĆčéčŗ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_CMD. ąĢčüą╗ąĖ ąŠčéą▓ąĄčé (ą║ąŠčĆąŠčéą║ąĖą╣ ąĖą╗ąĖ ą┤ą╗ąĖąĮąĮčŗą╣) ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐čĆąŠą▓ąĄčĆąŠčćąĮčŗą╣ ą║ąŠą┤ CRC, č鹊 ąŠčćąĖčēą░ąĄčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.CMDACT ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.RESPEND. ąĢčüą╗ąĖ ą┐čĆąŠą▓ąĄčĆą║ą░ CRC ą┐ąŠą║ą░ąĘą░ą╗ą░ ąŠčłąĖą▒ą║čā, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.CMDCRCFAIL. ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ąÆąĄčéą║ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ CRC ą║ąŠą╝ą░ąĮą┤čŗ. ąōąĄąĮąĄčĆą░č鹊čĆ CRC ą║ąŠą╝ą░ąĮą┤čŗ ą▓čŗčćąĖčüą╗čÅąĄčé 7-ą▒ąĖčéąĮčāčÄ ą║ąŠąĮčéčĆąŠą╗čīąĮčāčÄ čüčāą╝ą╝čā CRC ą┤ą╗čÅ ą▓čüąĄčģ 40 ą▒ąĖčé, ą┐čĆąĄą┤čłąĄčüčéą▓čāčÄčēąĖčģ ą║ąŠą┤čā CRC ą┤ą╗čÅ 48-ą▒ąĖčéąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ ąĖ 48-ą▒ąĖčéąĮčŗčģ ąŠčéą▓ąĄč鹊ą▓. ą¤čĆąŠą▓ąĄčĆčÅąĄą╝čŗąĄ ą▒ąĖčéčŗ ą▓ą║ą╗čÄčćą░čÄčé start-ą▒ąĖčé, čäą╗ą░ą│ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░, ąĖąĮą┤ąĄą║čü ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ą░čĆą│čāą╝ąĄąĮčé ą║ąŠą╝ą░ąĮą┤čŗ (ąĖą╗ąĖ čüčéą░čéčāčü ą║ą░čĆčéčŗ).

7-ą▒ąĖčéąĮą░čÅ ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ CRC ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆą▓čŗčģ 120 ą▒ąĖčé ą┐ąŠą╗čÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ą╗ąĖąĮąĮąŠą│ąŠ č乊čĆą╝ą░čéą░ ąŠčéą▓ąĄčéą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 start-ą▒ąĖčé, ą▒ąĖčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ 6 ą▒ąĖčé ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĖ CRC ą┤ą╗čÅ ą┤ą╗ąĖąĮąĮąŠą│ąŠ ąŠčéą▓ąĄčéą░. ąÜąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ CRC ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ąŠčéą▓ąĄčéą░ čŹč鹊 7-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą░ą╗ą│ąŠčĆąĖčéą╝čā.

CRC[6:0] = ą×čüčéą░č鹊ą║ (x7 * M(x))/G(x)

ąŚą┤ąĄčüčī G(x) = x7 + x3 + 1

ąöą╗čÅ ą┤ą╗ąĖąĮąĮąŠą│ąŠ ąŠčéą▓ąĄčéą░:

M(x) = x39 * (start-ą▒ąĖčé) + ... + x0 * (ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ą┐ąĄčĆąĄą┤ CRC)

ąöą╗čÅ ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąŠčéą▓ąĄčéą░:

M(x) = x19 * (start-ą▒ąĖčé) + ... + x0 * (ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ą┐ąĄčĆąĄą┤ CRC)

[ąśąĮč鹥čĆč乥ą╣čü ą┤ą░ąĮąĮčŗčģ RSI]

ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ RSI ąĖ ąĖąĘ RSI č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗čŗ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ RSI_D0..RSI_D7. ą©ąĖčĆąĖąĮą░ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ RSI ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ ą▒ąĖčé RSI_CTL.BUSWID. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čŹč鹊 1-ą▒ąĖčéąĮčŗą╣ čĆąĄąČąĖą╝ čłąĖąĮčŗ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_D0. 4-ą▒ąĖčéąĮčŗą╣ čĆąĄąČąĖą╝ ąĖą╗ąĖ 8-ą▒ąĖčéąĮčŗą╣ čĆąĄąČąĖą╝ ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąŠčüą╗ąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░čĆčéčŗ ą┤ą╗čÅ 4-ą▒ąĖčéąĮąŠą│ąŠ ąĖą╗ąĖ 8-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ.

ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą▓ąĄčéą║ąĖ ą┤ą░ąĮąĮčŗčģ RSI čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 RSI_CLK. ąŁčéą░ ą╝ą░čłąĖąĮą░ ą┐ąŠą║ąĖą┤ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ IDLE, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RSI_DATA_CTL.DATEN, čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ. ąĪąŠčüč鹊čÅąĮąĖąĄ, ą▓ ą║ąŠč鹊čĆąŠąĄ ą╝ą░čłąĖąĮą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ IDLE, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ RSI_DATA_CTL.DATDIR. ą¤čāčéčī ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤ą░ąĮąĮčŗčģ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčüčāąĮą║ąĄ ąĮąĖąČąĄ.

ąĀąĖčü. 24-5. ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ RSI.

ążą╗ą░ą│ąĖ čüčéą░čéčāčüą░ ą┐čāčéąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ.

ąóą░ą▒ą╗ąĖčåą░ 24-14. ążą╗ą░ą│ąĖ RSI_STATUS.

| ążą╗ą░ą│ RSI_XFRSTAT |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąĪąŠčüč鹊čÅąĮąĖąĄ, ą▓ ą║ąŠč鹊čĆąŠą╝ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ |

| TXACT |

ą¤čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ |

WAIT_S |

| RSI_XFRSTAT.RXACT |

ą¤čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ |

WAIT_R |

| RSI_XFRSTAT.DATBLKEND |

ąæą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ čāčüą┐ąĄčłąĮąŠ, ąĖ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé č鹊ą║ąĄąĮ CRC, ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čÄčēąĖą╣ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ.

ąæą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé čāčüą┐ąĄčłąĮąŠ, ąĖ ą┐čĆąŠčłąĄą╗ ą┐čĆąŠą▓ąĄčĆą║čā ąĮą░ CRC. |

BUSY (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░)

RECEIVE (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░) |

| RSI_XFRSTAT.DATCRCFAIL |

ą×čłąĖą▒ą║ą░ CRC ą▓ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą╝ ą▒ą╗ąŠą║ąĄ ą┤ą░ąĮąĮčŗčģ.

ą×čłąĖą▒ą║ą░ CRC ą▓ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą╝ ą▒ą╗ąŠą║ąĄ ą┤ą░ąĮąĮčŗčģ. |

SEND, ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░čåąĄą╗ąŠ ąĮą░ DATA_BLK_LGTH

BUSY, ąĄčüą╗ąĖ č鹊ą║ąĄąĮ CRC ą┐ąŠą║ą░ąĘą░ą╗ ąŠčłąĖą▒ą║čā |

| RSI_XFRSTAT.DATTO |

ą¤čĆąŠąĖąĘąŠčłąĄą╗ čéą░ą╣ą╝ą░čāčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą║ą░čĆčéą░ čüąĮčÅą╗ą░ čüąĖą│ąĮą░ą╗ ąĘą░ąĮčÅč鹊čüčéąĖ ąĮą░ RST_DAT0.

ą×čłąĖą▒ą║ą░ čéą░ą╣ą╝ą░čāčéą░ ą┐čĆąĖąĄą╝ą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ start-ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. |

BUSY

WAIT_R |

| RSI_XFRSTAT.DATEND |

ąÆčüąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ.

ąÆčüąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖąĮčÅčéčŗ. |

SEND

RECEIVE |

| RSI_XFRSTAT.SBITERR |

ąØąĄ ą▒čŗą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ start-ą▒ąĖčé ąĮą░ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ą░čģ RSI_DATAx. |

WAIT_R |

| RSI_XFRSTAT.TXFIFOSTAT |

FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ą┐ąŠą╗ąŠą▓ąĖąĮčā ą┐čāčüčé. |

SEND |

| RSI_XFRSTAT.TXFIFOFULL |

FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

SEND |

| RSI_XFRSTAT.TXFIFOZERO |

FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé. |

SEND |

| RSI_XFRSTAT.TXUNDR |

ą×čłąĖą▒ą║ą░ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ. |

SEND |

| RSI_XFRSTAT.TXFIFORDY |

ąÆ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╝ąĄčÄčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. |

SEND |

| RSI_XFRSTAT.RXFIFOSTAT |

FIFO ą┐čĆąĖąĄą╝ą░ ąĮą░ą┐ąŠą╗ąŠą▓ąĖąĮčā ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

RECEIVE |

| RSI_XFRSTAT.RXFIFOFULL |

FIFO ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

RECEIVE |

| RSI_XFRSTAT.RXFIFOZERO |

FIFO ą┐čĆąĖąĄą╝ą░ ą┐čāčüčé. |

RECEIVE |

| RSI_XFRSTAT.RXOVER |

ą×čłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO ą┐čĆąĖąĄą╝ą░. |

RECEIVE |

| RSI_XFRSTAT.RXFIFORDY |

ąÆ FIFO ą┐čĆąĖąĄą╝ą░ ąĖą╝ąĄčÄčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. |

RECEIVE |

ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą║ą░čĆčéčā. ąÉą╗ą│ąŠčĆąĖčéą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠčüč鹊ąĖčé ąĖąĘ čüąŠčüč鹊čÅąĮąĖą╣ WAIT_S, SEND ąĖ BUSY. ąĀąĄą│ąĖčüčéčĆčŗ RSI_BLKSZ, RSI_DATA_LEN ąĖ RSI_DATA_TMR ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ ą┐čāčéąĖ ą┤ą░ąĮąĮčŗčģ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ RSI_DATA_CTL. ą¤čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ IDLE ąĖ ą▓čģąŠą┤ąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT_S ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäą╗ą░ą│ RSI_XFRSTAT.TXACT ąĖ ą║ąŠą┐ąĖčĆčāąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ RSI_DATA_LEN ą▓ čĆąĄą│ąĖčüčéčĆ RSI_DATA_CNT.

ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ SEND ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ.

ŌĆó Stream transfer mode - ąĄčüą╗ąĖ RSI ą▒čŗą╗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąŠč鹊ą║ąŠą▓ąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 ąŠąĮ ą┐ąŠčüčŗą╗ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ ą║ą░čĆčéčā, ą┐ąŠą║ą░ ąĮąĄ ąŠą▒ąĮčāą╗ąĖčéčüčÅ čüč湥čéčćąĖą║ RSI_DATA_CNT, ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATEND, ąĖ ą╝ą░čłąĖąĮą░ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄčģąŠą┤ RSI_DATA_CNT ą▓ 0 ą░ą║čéąĖą▓ąĖčĆčāąĄčé ą╝ą░čłąĖąĮčā ą┐čāčéąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ąŠą╝ą░ąĮą┤čŗ, ąĄčüą╗ąĖ ąŠąĮą░ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ PEND. ąĢčüą╗ąĖ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą┐ąŠč鹊ą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čāčüčéčŗą╝, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ą▓ FIFO ą▓ ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.TXUNDR ą┐ąĄčĆąĄą┤ ą▓ąŠąĘą▓čĆą░č鹊ą╝ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ŌĆó Block transfer mode - ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ RSI_BLKSZ ą▒ą░ą╣čé, ą║ą░ą║ čŹč鹊 čāą║ą░ąĘą░ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ RSI_DATA_CTL. ąÜą░ąČą┤čŗą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▒ą░ą╣čé čéą░ą║ąČąĄ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčé čüč湥čéčćąĖą║ RSI_DATA_CNT.

ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░ RSI ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčé ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čāčÄ ą▓ąĮčāčéčĆąĖ čüąĄą▒čÅ ą║ąŠąĮčéčĆąŠą╗čīąĮčāčÄ čüčāą╝ą╝čā CRC16 ąĖ end-ą▒ąĖčé ą║ ą┤ą░ąĮąĮčŗą╝, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╝ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗čŗ RSI_D0..RSI_D7.

ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ RSI ąŠąČąĖą┤ą░ąĄčé ąŠčé ą║ą░čĆčéčŗ č鹊ą║ąĄąĮą░ ąŠčéą▓ąĄčéą░ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_D0, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ąČąĄčé, ą▒čŗą╗ąĖ ą╗ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐čĆąĖąĮčÅčéčŗ ą┤ą░ąĮąĮčŗąĄ ą║ą░čĆč鹊ą╣, ąĖą╗ąĖ ąĮąĄčé. ąĢčüą╗ąĖ č鹊ą║ąĄąĮ ąŠčéą▓ąĄčéą░ CRC ą║ą░čĆčéčŗ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐čĆąĖąĮčÅčéčŗ ą║ą░čĆč鹊ą╣, č鹊 ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ą╝ą░čłąĖąĮčŗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ BUSY čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATBLKEND. ąĢčüą╗ąĖ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą▒čŗą╗ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐čĆąĖąĮčÅčéčŗ ą║ą░čĆč鹊ą╣, č鹊 ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATCRCFAIL.

ąÜąŠą│ą┤ą░ ą┤ąĄą║čĆąĄą╝ąĄąĮčé čüč湥čéčćąĖą║ą░ RSI_DATA_CNT ą┤ąŠčüčéąĖą│ąĮąĄčé 0, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATEND. ąĢčüą╗ąĖ ąŠą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé, ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ č鹥ą║čāčēąĄą│ąŠ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ RSI_DATA_CNT ą┤ąŠčüčéąĖą│ 0, ąĖ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ąĮąĄ čĆą░ą▓ąĮąŠ RSI_BLKSZ, ą┐ąĄčĆąĄą┤ą░čćą░ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATCRCFAIL.

ąÆąĄčéą║ą░ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤ą░ąĮąĮčŗčģ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE. ąĢčüą╗ąĖ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐čāčüčéčŗą╝, ą║ąŠą│ą┤ą░ ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠąĖąĘąŠą╣čéąĖ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, č鹊 ą┐ąĄčĆąĄą┤ ą▓ąŠąĘą▓čĆą░č鹊ą╝ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.TXUNDR.

ąÆąŠ ą▓čĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅ BUSY ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčé čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ RSI_D0, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą╗ąŠą│ąĖč湥čüą║ąĖą╝ ąĮčāą╗ąĄą╝, čćč鹊 ą║ą░čĆčéą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąĘą░ąĮčÅč鹊čüčéąĖ. ąÜąŠą│ą┤ą░ ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 ąĮą░ RSI_D0, č鹊 ą║ą░čĆčéą░ ą▒ąŠą╗čīčłąĄ ąĮąĄ ąĘą░ąĮčÅčéą░, ąĖ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT_S. ąóąŠą│ą┤ą░ ą╝ą░čłąĖąĮą░ ą▓ąĄčĆąĮąĄčéčüčÅ ą╗ąĖą▒ąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE, ąĄčüą╗ąĖ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ, ąĖą╗ąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ SEND, čćč鹊ą▒čŗ ąĮą░čćą░ą╗ą░čüčī ą┐ąĄčĆąĄą┤ą░čćą░ ą┤čĆčāą│ąŠą│ąŠ ą▒ą╗ąŠą║ą░.

ąØą░ ą▓čģąŠą┤ąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ BUSY ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ąĮą░čćąĖąĮą░ąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ čéą░ą╣ą╝ą░čāčéą░, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSI_DATA_TMR. ąĢčüą╗ąĖ čüč湥čéčćąĖą║ čéą░ą╣ą╝ą░čāčéą░ RSI ąŠą▒ąĮčāą╗ąĖą╗čüčÅ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čüąĖą│ąĮą░ą╗ RSI_D0 ą┐ąĄčĆąĄčłąĄą╗ ą▓ ą╗ąŠą│. 1, č鹊 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ RSI_XFRSTAT.DATTO ąĖ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ą¤čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ąŠčé ą║ą░čĆčéčŗ. ąÉą╗ą│ąŠčĆąĖčéą╝ ą┐čĆąĖąĄą╝ą░ čüąŠčüč鹊ąĖčé ąĖąĘ čüąŠčüč鹊čÅąĮąĖą╣ WAIT_R ąĖ RECEIVE. ąöąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ RSI_BLKSZ, RSI_DATA_LEN ąĖ RSI_DATA_TMR ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ RSI_DATA_CTL. ą¤čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ IDLE ąĖ ą▓čģąŠą┤ąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT_R ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ RSI_XFRSTAT.RXACT ąĖ čüą║ąŠą┐ąĖčĆčāąĄčé RSI_DATA_LEN ą▓ RSI_DATA_CNT. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ RECEIVE ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆąĄąČąĖą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą░ą╗ą│ąŠčĆąĖčéą╝ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĖąĄą╝ą░ ą▓ąŠčłąĄą╗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT_R ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐čĆąĖąĄą╝ą░, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ąĮą░čćąĖčéą░ąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ čéą░ą╣ą╝ą░čāčéą░, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSI_DATA_TMR.

ąĢčüą╗ąĖ RSI ą▒čŗą╗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ 1-ą▒ąĖčéąĮąŠą╣ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATTO, ąĄčüą╗ąĖ start-ą▒ąĖčé ąĮąĄ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_D0 ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čüč湥čéčćąĖą║ ąŠą▒ąĮčāą╗ąĖą╗čüčÅ čéą░ą╣ą╝ą░čāčéą░. ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ąĢčüą╗ąĖ RSI ą▒čŗą╗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ 4-ą▒ąĖčéąĮąŠą╣ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ąĖ start-ą▒ąĖčé ąĮąĄ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮą░ ą▓čüąĄčģ č湥čéčŗčĆąĄčģ čüąĖą│ąĮą░ą╗ą░čģ RSI_D0..RSI_D3 ą┐ąĄčĆąĄą┤ ąŠą▒ąĮčāą╗ąĄąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ą░čāčéą░, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATTO. ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE. ąĢčüą╗ąĖ start-ą▒ąĖčé ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮą░ ąĮąĄą║ąŠč鹊čĆčŗčģ, ąĮąŠ ąĮąĄ ą▓čüąĄčģ, čüąĖą│ąĮą░ą╗ą░čģ RSI_D0..RSI_D3 ąĮą░ ąŠą┤ąĮąŠą╝ ąĖ č鹊ą╝ ąČąĄ čéą░ą║č鹥 ą▓čŗą▒ąŠčĆą║ąĖ, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.SBITERR, ąĖ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE. ą¤čĆąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠą╝ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĖ start-ą▒ąĖčéą░ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ RECEIVE.

ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ RECEIVE ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠč鹊čćąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą▒ą╗ąŠčćąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ŌĆó Stream transfer mode - ą┤ą╗čÅ ą┐ąŠč鹊ą║ąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ čāą┐ą░ą║ąŠą▓čŗą▓ą░čÄčéčüčÅ ą▓ ą▒ą░ą╣čéčŗ ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ FIFO ą┤ą░ąĮąĮčŗčģ. ąöą░ąĮąĮčŗąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ FIFO ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą║ą░ ą┤ąĄą║čĆąĄą╝ąĄąĮčé čüč湥čéčćąĖą║ą░ RSI_DATA_CNT ąĮąĄ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĮčāą╗čÅ.

ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĮčāą╗čÅ, ąŠčüčéą░ą▓čłąĖąĄčüčÅ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ąĘą░ą┐ąĖčłčāčéčüčÅ ą▓ FIFO, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATEND, ąĖ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT_R.

ąÜąŠą│ą┤ą░ ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, čćč鹊 FIFO ą┐čĆąĖąĄą╝ą░ ą┐čāčüčé, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.RXFIFOZERO, ąĖ ą╝ą░čłąĖąĮą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE. ąĢčüą╗ąĖ FIFO ą┤ą░ąĮąĮčŗčģ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╝, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą▒čŗą╗ąĖ ą▓čŗą▒čĆą░ąĮčŗ (ą┐čĆąŠčćąĖčéą░ąĮčŗ) ąĖąĘ ąĮąĄą│ąŠ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▓ FIFO ąĘą░ą┐ąĖčłąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ą╣čé, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.RXOVER. ąóąŠą│ą┤ą░ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą▓ą╝ąĄčüč鹊 WAIT_R ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ŌĆó Block transfer mode - ą▓ čĆąĄąČąĖą╝ąĄ ą▒ą╗ąŠčćąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ čāą┐ą░ą║ąŠą▓čŗą▓ą░čÄčéčüčÅ ą▓ ą▒ą░ą╣čéčŗ ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ FIFO ą┤ą░ąĮąĮčŗčģ.

ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅč鹊 RSI_BLKSZ ą▒ą░ą╣čé, RSI čćąĖčéą░ąĄčé ą▒ąĖčéčŗ CRC16. ąĢčüą╗ąĖ ą┐čĆąĖąĮčÅčéą░čÅ CRC čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą▓čŗčćąĖčüą╗ąĄąĮąĮąŠą╣ ą▓ąĮčāčéčĆąĖ CRC, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATBLKEND ąĖ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ WAIT_R.

ąĢčüą╗ąĖ čüč湥čéčćąĖą║ RSI_DATA_CNT ąĖčüč鹥ą║ ąĮą░ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĖ ą┐ąŠ ą║ąŠąĮčåčā ą▒ą╗ąŠą║ą░ RSI_BLKSZ, čāčüčéą░ąĮąŠą▓čÅčéčüčÅ čäą╗ą░ą│ąĖ RSI_XFRSTAT.DATEND ąĖ RSI_XFRSTAT.DATBLKEND, ąĖ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ WAIT_R.

ąÜąŠą│ą┤ą░ ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, čćč鹊 FIFO ą┐čĆąĖąĄą╝ą░ ą┐čāčüčé, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.RXFIFOZERO, ąĖ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ IDLE. ąĢčüą╗ąĖ čüč湥čéčćąĖą║ RSI_DATA_CNT ąŠą▒ąĮčāą╗ąĖą╗čüčÅ ą┤ąŠ ą║ąŠąĮčåą░ ą▒ą╗ąŠą║ą░ RSI_BLKSZ, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RSI_XFRSTAT.DATCRCFAIL. ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ IDLE.

ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ CRC ą┤ą░ąĮąĮčŗčģ. ąōąĄąĮąĄčĆą░č鹊čĆ CRC ą┤ą░ąĮąĮčŗčģ ą▓čŗčćąĖčüą╗čÅąĄčé 16-ą▒ąĖčéąĮčāčÄ ą║ąŠąĮčéčĆąŠą╗čīąĮčāčÄ čüčāą╝ą╝čā ą┤ą╗čÅ ą▓čüąĄčģ ą▒ąĖčé, ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ąĖą╗ąĖ ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą╗čÅ ąĖą╝ąĄčÄčēąĄą╣čüčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą▒ą╗ąŠą║ą░ (ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┐ąŠč鹊ą║ą░ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ). ąöą╗čÅ 1-ą▒ąĖčéąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čłąĖąĮčŗ CRC16 ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┤ą╗čÅ ą▓čüąĄčģ ą┤ą░ąĮąĮčŗčģ, ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_D0. ąöą╗čÅ 4-ą▒ąĖčéąĮąŠą╣ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ CRC16 ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ RSI_D0..RSI_D3. ąÜąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ ą┤ą░ąĮąĮčŗčģ čŹč鹊 16-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą▓čŗčćąĖčüą╗čÅąĄą╝ąŠąĄ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝.

CRC[15:0] = ą×čüčéą░č鹊ą║ (x16 * M(x))/G(x)

ąŚą┤ąĄčüčī:

G(x) = x16 + x12 + x5 + 1

M(x) = x((8 * DTX_BLK_LGTH) ŌĆō 1) * (ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ) + ... + x0 * (ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ)

[RSI Data FIFO]

FIFO ą┤ą░ąĮąĮčŗčģ ąĖą╝ąĄąĄčé ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ 32-ą▒ąĖčéąĮąŠą╣ čłąĖčĆąĖąĮčŗ ąĖ ą│ą╗čāą▒ąĖąĮčŗ ąĖąĘ 16 čüą╗ąŠą▓. ą×ąĮ čĆą░ą▒ąŠčéą░ąĄčé čü ą╗ąŠą│ąĖą║ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ FIFO ąĘą░ą▓ąĖčüąĖčé ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ čäą╗ą░ą│ąŠą▓ RSI_XFRSTAT.TXACT ąĖ RSI_XFRSTAT.RXACT. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ RSI_XFRSTAT.TXACT, č鹊 FIFO čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÅ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ RSI ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą▓ ą║ą░čĆčéčā. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ RSI_XFRSTAT.RXACT, č鹊 FIFO čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ FIFO ą┐čĆąĖąĄą╝ą░, ą│ą┤ąĄ RSI ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▓ ąĮąĄą│ąŠ ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąĖąĮčÅčéčŗąĄ ąŠčé ą║ą░čĆčéčŗ. ąĢčüą╗ąĖ ąĮąĖ ąŠą┤ąĖąĮ ąĖąĘ čŹčéąĖčģ čäą╗ą░ą│ąŠą▓ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čĆą░ą▒ąŠčéą░ FIFO ąĘą░ą┐čĆąĄčēąĄąĮą░.

ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░ čĆą░ą▒ąŠčéą░ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ, ą▓čüąĄ čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ, ąĖ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą▓ 0 ą▓čüąĄ čāą║ą░ąĘą░č鹥ą╗ąĖ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ. RSI ą▓čŗčüčéą░ą▓ą╗čÅąĄčé čäą╗ą░ą│ RSI_XFRSTAT.TXACT ą┐čĆąĖ čüčéą░čĆč鹥 ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╗ąŠą│ąĖą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ čéą░ą║, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ.

ąóą░ą▒ą╗ąĖčåą░ 24-15. ążą╗ą░ą│ąĖ čüčéą░čéčāčüą░ RSI Transmit FIFO.

| ążą╗ą░ą│RSI_XFRSTAT |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| RSI_XFRSTAT.TXFIFOSTAT |

FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ą┐ąŠą╗ąŠą▓ąĖąĮčā ą┐čāčüčé. |

| RSI_XFRSTAT.TXFIFOFULL |

FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

| RSI_XFRSTAT.TXFIFOZERO |

FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé. |

| RSI_XFRSTAT.TXUNDR |

ą×čłąĖą▒ą║ą░ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ. |

| RSI_XFRSTAT.TXFIFORDY |

ąÆ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╝ąĄčÄčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. |

ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░ čĆą░ą▒ąŠčéą░ FIFO ą┐čĆąĖąĄą╝ą░, ą▓čüąĄ čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ ą┐čĆąĖąĄą╝ą░ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ, ąĖ čāą║ą░ąĘą░č鹥ą╗ąĖ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą▓ 0. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ RSI ą▓čŗčüčéą░ą▓ą╗čÅąĄčé čäą╗ą░ą│ RXACT ą┐čĆąĖ čüčéą░čĆč鹥 čéčĆą░ąĮąĘą░ą║čåąĖąĖ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╗ąŠą│ąĖą║ą░ ą┐čĆąĖąĄą╝ą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ FIFO ą┐čĆąĖąĄą╝ą░ čéą░ą║, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ.

ąóą░ą▒ą╗ąĖčåą░ 24-16. ążą╗ą░ą│ąĖ čüčéą░čéčāčüą░ RSI Receive FIFO.

| ążą╗ą░ą│RSI_XFRSTAT |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| RSI_XFRSTAT.RXFIFOSTAT |

FIFO ą┐čĆąĖąĄą╝ą░ ąĮą░ą┐ąŠą╗ąŠą▓ąĖąĮčā ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

| RSI_XFRSTAT.RXFIFOFULL |

FIFO ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

| RSI_XFRSTAT.RXFIFOZERO |

FIFO ą┐čĆąĖąĄą╝ą░ ą┐čāčüčé. |

| RSI_XFRSTAT.RXOVER |

ą×čłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO ą┐čĆąĖąĄą╝ą░. |

| RSI_XFRSTAT.RXFIFORDY |

ąÆ FIFO ą┐čĆąĖąĄą╝ą░ ąĖą╝ąĄčÄčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. |

[ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ąĘą░ąĮčÅč鹊čüčéąĖ/ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą║ą░čĆčéčŗ (Busy/Ready)]

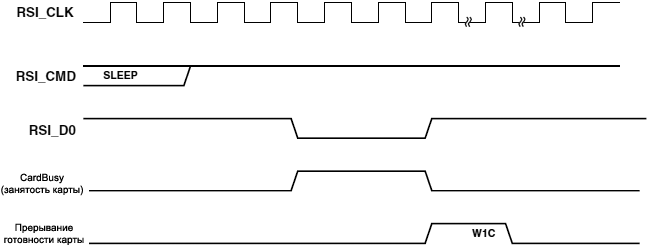

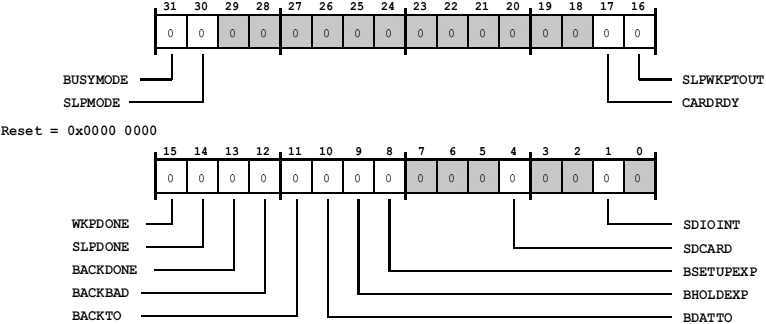

ąØąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ, ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ CMD6, ą╝ąŠą│čāčé ą▓čŗčüčéą░ą▓ą╗čÅčéčī čüąĖą│ąĮą░ą╗ ąĘą░ąĮčÅč鹊čüčéąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ RSI_D0 signal ą▓ ą╗ąŠą│. 0 č湥čĆąĄąĘ 2 čéą░ą║čéą░ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ end-ą▒ąĖčéą░ ą║ąŠą╝ą░ąĮą┤čŗ. ąŻčüčéą░ąĮąŠą▓ą║ą░ RSI_CMD.CHKBUSY ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé RSI ą┐čĆąŠą▓ąĄčĆčÅčé ąĮą░ą╗ąĖčćąĖąĄ čüąĖą│ąĮą░ą╗ą░ ąĘą░ąĮčÅč鹊čüčéąĖ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čüąĖą│ąĮą░ą╗čŗ RSI_D1..RSI_D3 čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą║ą░čĆč鹊ą╣, čģąŠčéčÅ ąĖčģ čüąŠčüč鹊čÅąĮąĖąĄ ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖąĄ.

ąĢčüą╗ąĖ ą▒ąĖčé RSI_CMD.CHKBUSY čĆą░ąĘčĆąĄčłąĄąĮ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣, č鹊 ąĮą░ čéčĆąĄčéčīąĄą╝ čéą░ą║č鹥 ą┐ąŠčüą╗ąĄ end-ą▒ąĖčéą░ ą║ąŠą╝ą░ąĮą┤čŗ čüąĖą│ąĮą░ą╗ RSI_D0 ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ąĮą░čģąŠą┤ąĖčéčüčÅ ą╗ąĖ ąŠąĮ ą▓ ą╗ąŠą│. 0. ąĢčüą╗ąĖ RSI_D0 ą▓ ą╗ąŠą│. 0, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RSI_STAT0.BUSYMODE. ąÜąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ RSI_D0 ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RSI_STAT0.CARDRDY (čŹč鹊čé ą▒ąĖčé čéąĖą┐ą░ W1C, čé. ąĄ. čćč鹊ą▒čŗ ąĄą│ąŠ ąŠčćąĖčüčéąĖčéčī, ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▓ ąĮąĄą│ąŠ ąĄą┤ąĖąĮąĖčåčā), ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé RSI_STAT0.BUSYMODE, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą║ą░čĆčéą░ (ready interrupt).

ąĢčüą╗ąĖ RSI_D0 ąĮąĄ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0 ąĮą░ čéčĆąĄčéčīąĄą╝ čéą░ą║č鹥 ą┐ąŠčüą╗ąĄ end-ą▒ąĖčéą░, č鹊 čüčćąĖčéą░ąĄčéčüčÅ, čćč鹊 ą║ą░čĆčéą░ ąĮąĄ ąĘą░ąĮčÅčéą░. ąæąĖčé RSI_STAT0.BUSYMODE čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ čüąŠčüč鹊čÅąĮąĖčÅ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ RSI ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą║ą░čĆčéčŗ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RSI_STAT0.CARDRDY. ąĢčüą╗ąĖ ą▒ąĖčé RSI_CMD.CHKBUSY ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮ, čüąĖą│ąĮą░ą╗ RSI_D0 ąĮąĄ ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ ąĮą░ čāčüą╗ąŠą▓ąĖąĄ ąĘą░ąĮčÅč鹊čüčéąĖ.

ąæąĖčé RSI_STAT0.BUSYMODE čéą░ą║ąČąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ, ąĄčüą╗ąĖ čüąĖą│ąĮą░ą╗ RSI_D0 ą┐čĆąĖčéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą║ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą║ą░čĆčéą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą┤ą░ąĮąĮčŗąĄ ąĮą░ čüą▓ąŠą╣ ąĮąŠčüąĖč鹥ą╗čī. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ąĖčé RSI_STAT0.CARDRDY ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą║ą░čĆčéčŗ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ąĮčÅč鹊čüčéąĖ (busy timing) ą║ą░čĆčéčŗ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ.

ąĀąĖčü. 24-6. ąĀą░ą▒ąŠčéą░ ąĖąĮą┤ąĖą║ą░čåąĖąĖ ąĘą░ąĮčÅč鹊čüčéąĖ ą║ą░čĆčéčŗ (Card Busy).

[ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ SDIO]

ąöą▓ąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čäčāąĮą║čåąĖąĖ RSI čĆąĄą░ą╗ąĖąĘčāčÄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī SDIO.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ RSI_D0.

ŌĆó ąŚą░ą┐čĆąŠčü ąŠąČąĖą┤ą░ąĮąĖčÅ čćč鹥ąĮąĖčÅ (Read wait request) č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ RSI_D2.

ąŻčüčéčĆąŠą╣čüčéą▓ą░ SDIO ą╝ąŠą│čāčé ąĖą╝ąĄčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ąŠą┤ąĮąŠą╣ ą╗ąĖąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čÅą▓ą╗čÅąĄčéčüčÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗą╝ ą║ čāčĆąŠą▓ąĮčÄ (ąĮąĄ ą║ ą┐ąĄčĆąĄą┐ą░ą┤čā), ą┐ąŠąĘą▓ąŠą╗čÅčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ čäčāąĮą║čåąĖčÅą╝ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ, ą┐ąŠą║ą░ ą▓čüąĄ ąĖčüč鹊čćąĮąĖą║ąĖ, ą║ąŠč鹊čĆčŗąĄ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĮąĄ ą▒čāą┤čāčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ąĖ ąŠčćąĖčēąĄąĮčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ RSI.

ąÆčüąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░ą╣ą┤ąĄąĮčŗ ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░ SDIO. ąŁčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčćąĖčēą░čÄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ, čāąĮąĖą║ą░ą╗čīąĮčŗą╝ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ čäčāąĮą║čåąĖąĖ.

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ SDIO ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā RSI, ą▓čüčéą░ą▓ą╗čÅčÅ čüąĖą│ąĮą░ą╗ RSI_D1 ą▓ ą╗ąŠą│. 0. ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▒ąĖčé RSI_STAT0.SDIOINT. ąŁč鹊čé čüčéą░čéčāčü ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▒ąĖč鹊ą╝ RSI_IMSK0.SDIOINT, čćč鹊ą▒čŗ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąÜąŠą│ą┤ą░ RSI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ 1-ą▒ąĖčéąĮąŠą╣ čłąĖąĮčŗ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠąĄ SDIO, ąĮąĄ ąĖą╝ąĄąĄčé ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 RSI_D1 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗, ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ ą┐ąŠą┤ čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ IRQ. RSI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖč鹊ą▓ RSI_CFG.DATPUP, ą║ąŠč鹊čĆčŗąĄ čĆą░ąĘčĆąĄčłą░čÄčé ą▓ąĄčĆčģąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮčŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ pull-up ąĮą░ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ą░čģ RSI_D0..RSI_D7. ąÜąŠą│ą┤ą░ RSI ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ą╗ąŠą│. 0 ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RSI_D1, RSI ą▓čŗčüčéą░ą▓ą╗čÅąĄčé čäą╗ą░ą│ RSI_STAT0.SDIOINT. ąŁč鹊čé čäą╗ą░ą│ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ, ą┐ąŠą║ą░ čüąĖą│ąĮą░ą╗ RSI_D1 ąĮąĄ ą▓ąĄčĆąĮąĄčéčüčÅ čüąĮąŠą▓ą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1.

ąÜąŠą│ą┤ą░ RSI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ 4-ą▒ąĖčéąĮąŠą╣ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, čüąĖą│ąĮą░ą╗ RSI_D1 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĮąŠ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ąŠą╝ IRQ ąĖ čüąĖą│ąĮą░ą╗ąŠą╝ RSI_D1. ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░čüą┐ąŠąĘąĮą░ąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ RSI č鹊ą╗čīą║ąŠ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

[ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ RSI]

ąĪą╗ąĄą┤čāčÄčēąĖąĄ čüąĄą║čåąĖąĖ ąŠą┐ąĖčüčŗą▓ą░čÄčé čäčāąĮą║čåąĖąŠąĮą░ą╗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ RSI ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ čĆą░ą▒ąŠčéčŗ.

Card Identification Mode. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ą║ą░čĆčéą░) ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą║ RSI, ą▓ą┐ąĄčĆą▓čŗąĄ ąĮą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┤ą░ąĮąŠ ą┐ąĖčéą░ąĮąĖąĄ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ čģąŠčüč鹊ą╝ ąĖą╗ąĖ čüą▒čĆąŠčłąĄąĮąŠ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüąĮą░čćą░ą╗ą░ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąŠ ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąŠ čģąŠčüč鹊ą╝. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠ ą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ čü ą║ąŠąĮčéčĆąŠą╗ąĄčĆąŠą╝ RSI, ąĖ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ąĖ ą┤čĆą░ą╣ą▓ąĄčĆą░ą╝ąĖ. ąŁčéą░ čäą░ąĘą░ čĆą░ą▒ąŠčéčŗ čü ą║ą░čĆč鹊ą╣ ąŠą▒čēąĄąĖąĘą▓ąĄčüčéąĮą░ ą║ą░ą║ čĆąĄąČąĖą╝ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą║ą░čĆčéčŗ (card identification mode).

ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą║ą░čĆčéčŗ, ąŠčé čģąŠčüčéą░ ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ.

ŌĆó ąĪą▒čĆąŠčü čāčüčéčĆąŠą╣čüčéą▓ą░

ŌĆó ą¤čĆąŠą▓ąĄčĆąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü ąĖą╝ąĄčÄčēąĖą╝čüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ

ŌĆó ąśą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čéąĖą┐ čāčüčéčĆąŠą╣čüčéą▓ą░

ŌĆó ąØą░ąĘąĮą░čćąĖčéčī čāčüčéčĆąŠą╣čüčéą▓čā (ą║ą░čĆč鹥) / ąĘą░ą┐čĆąŠčüąĖčéčī čā ąĮąĄą│ąŠ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą║ą░čĆčéčŗ (relative card address, RCA)

ąÆąĄčüčī ąŠą▒ą╝ąĄąĮ ąĖąĮč乊čĆą╝ą░čåąĖąĄą╣ ą╝ąĄąČą┤čā čģąŠčüč鹊ą╝ ąĖ ą║ą░čĆč鹊ą╣ ą▓ąŠ ą▓čĆąĄą╝čÅ čäą░ąĘčŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą║ą░čĆčéčŗ ą┐čĆąŠąĖčüčģąŠą┤čÅčé č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ RSI_CMD. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą▓ąŠ ą▓čĆąĄą╝čÅ čäą░ąĘčŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ąŠą▒čŗčćąĮąŠ ąĮą░ą╝ąĮąŠą│ąŠ ąĮąĖąČąĄ, č湥ą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą║ą░čĆčéčŗ ą▓ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ ą║ą░čĆčéčŗ.

Data Transfer Mode. ąÜą░čĆčéą░ ą▓ąŠą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (stand-by), ąĖąĘą▓ąĄčüčéąĮąŠąĄ ą║ą░ą║ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (data transfer mode), ą║ąŠą│ą┤ą░ ąĄą╣ ą▒čāą┤ąĄčé ąĮą░ąĘąĮą░č湥ąĮ ą░ą┤čĆąĄčü RCA. ą¤ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąŠą│čāčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ąŠčłą╗ąŠ ą▓ data transfer mode.

ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄčłą╗ąŠ ą▓ data transfer mode, ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ č湥čĆąĄąĘ RSI_CMD ąĖ RSI_D0..RSI_D7. ąÜą░čĆčéą░ ą┤ą░ą╗ąĄąĄ ąŠą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čłąĖčĆąĖąĮčŗ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĖ ąĄą╝ą║ąŠčüčéąĖ ą┐ą░ą╝čÅčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆ čŹč鹊ą╝ ą╝ąĄčüč鹥 čłąĖčĆąĖąĮčā čłąĖąĮčŗ ą╝ąŠąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī, ąĖ ą╝ąŠąČąĮąŠ čāą▓ąĄą╗ąĖčćąĖčéčī čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā čłąĖąĮčŗ.

ąöą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ ąĮąĄą│ąŠ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüą╗ąĄą┤čāčÄčēąĖčģ 2 ą╝ąĄč鹊ą┤ąŠą▓.

ŌĆó ą¤ąŠč鹊ą║ąŠą▓čŗąĄ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ. ą¤ąŠč鹊ą║ąŠą▓čŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░čÄčé ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą║ą░ RSI ąĮąĄ ąŠčüčéą░ąĮąŠą▓ąĖčé ą┐ąĄčĆąĄą┤ą░čćčā čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣. ąöą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐ąŠč鹊čćąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čĆą░ą▒ąŠčćčāčÄ čćą░čüč鹊čéčā. ą¤ąŠč鹊ą║ąŠą▓čŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą╝ąŠą│čāčé čéą░ą║ąČąĄ ąĖą╝ąĄčéčī ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ, ąĘą░ą▓ąĖčüčÅčēąĖąĄ ąŠčé ą│čĆą░ąĮąĖčå ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą╗ąŠą║ą░.

ŌĆó ąæą╗ąŠčćąĮčŗąĄ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ. ą¤ąĄčĆąĄą┤ą░čćąĖ, ąŠčüąĮąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ ą▒ą╗ąŠą║ąĄ ą┐čĆąĖą▓ąĄą┤čāčé ą║ č鹊ą╝čā, čćč鹊 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą┤ą░čćą░ ą▒ą╗ąŠą║ą░ ąĘą░čĆą░ąĮąĄąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░.

ąĀą░ąĘą╝ąĄčĆ ą▒ą╗ąŠą║ą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░ (ą║ą░čĆčéčŗ SD), ąĖ ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ RSI ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéčīčÄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┤ą▓čāą╝čÅ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ, ąŠą┐ąĖčüą░ąĮąĮčŗą╝ąĖ ąĮąĖąČąĄ.

DMA Data Transfer. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā RSI ąĮą░ąĘąĮą░č湥ąĮ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą║ą░ąĮą░ą╗ DMA. ąŁč鹊čé ą║ą░ąĮą░ą╗ DMA ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą╗ąĖą▒ąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą╗ąĖą▒ąŠ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ FIFO ą┤ą░ąĮąĮčŗčģ RSI / ą▓ FIFO ą┤ą░ąĮąĮčŗčģ RSI. ą¤čĆąĖ čŹč鹊ą╝ ą┐ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé čüąŠą▓ąĄčĆčłą░čéčīčüčÅ ą▒ąĄąĘ čāčćą░čüčéąĖčÅ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

Core Data Transfer. ąĢčüą╗ąĖ ą║ą░ąĮą░ą╗ RSI DMA ąĘą░ą┐čĆąĄčēąĄąĮ, č鹊 FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ąĖą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮ čÅą┤čĆąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ RSI_FIFO, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗą╣ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (memory-mapped register, MMR). ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (overflow) ąĖą╗ąĖ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ (underflow) FIFO, čÅą┤čĆąŠ ą┤ąŠą╗ąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ FIFO ąŠą┤ąĮąĖą╝ ąĖąĘ ą┤ą▓čāčģ čüą╗ąĄą┤čāčÄčēąĖčģ čüą┐ąŠčüąŠą▒ąŠą▓.

1. ąöąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ (RSI_XFR_IMSK0.TXFIFOZERO, RSI_XFR_IMSK1.TXFIFOZERO) ąĖą╗ąĖ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO ą┐čĆąĖąĄą╝ą░ (RSI_XFR_IMSK0.RXFIFOFULL, RSI_XFR_IMSK1.RXFIFOFULL). ąÆ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ ą▓ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĮčÅč鹊ąĄ čüą╗ąŠą▓ąŠ ą▓čŗčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąĖąĘ FIFO ą┐čĆąĖąĄą╝ą░.

2. ą×ą┐čĆąŠčü (ą┐ąŠą╗ą╗ąĖąĮą│) ą▒ąĖč鹊ą▓ čüčéą░čéčāčüą░ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ (RSI_XFRSTAT.TXFIFOZERO) ąĖą╗ąĖ ą▒ąĖč鹊ą▓ čüčéą░čéčāčüą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO ą┐čĆąĖąĄą╝ą░ (RSI_XFRSTAT.RXFIFOFULL). ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝ąŠąĄ čüą╗ąŠą▓ąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĮčÅč鹊ąĄ čüą╗ąŠą▓ąŠ ą▓čŗčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąĖąĘ FIFO ą┐čĆąĖąĄą╝ą░.

Boot Mode. ąÜą░čĆčéčŗ ą╝čāą╗čīčéąĖą╝ąĄą┤ąĖą░ (MultiMedia Cards, MMC) ąŠčüąĮąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅčģ MMCA version 4.3 ąĖą╗ąĖ ą▒ąŠą╗ąĄąĄ ą┐ąŠąĘą┤ąĮąĖčģ, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, ąĖąĘą▓ąĄčüčéąĮčŗą╣ ą║ą░ą║ čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ (boot mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čģąŠčüčé MMC ą╝ąŠąČąĄčé čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ MMC, čāą┤ąĄčƹȹĖą▓ą░čÅ čüąĖą│ąĮą░ą╗ RSI_CMD ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0 ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą║ą░čĆčéčŗ (power-on), ąĖą╗ąĖ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ CMD0 čü ą░čĆą│čāą╝ąĄąĮč鹊ą╝ 0xFFFFFFFA (ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░), ą┐ąĄčĆąĄą┤ ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ CMD1. ąöą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą╗ąĖą▒ąŠ ąĖąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ (dedicated boot area), ąĖą╗ąĖ ąĖąĘ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (user area).

Normal Boot Mode. ą¤ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ąŠą▒čŗčćąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ (normal boot mode) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▒ąĖčéčŗ čüč湥čéčćąĖą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_BOOT_TCNTR.SETUP ąĖ RSI_BOOT_TCNTR.HOLD) ąĖ ą▒ąĖčé čéąĖą┐ą░ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_CFG.MMCBMODE=0). ąśąĮą░č湥 RSI ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓ 74 ąĖ 56 čéą░ą║č鹊ą▓ RSI_CLK.

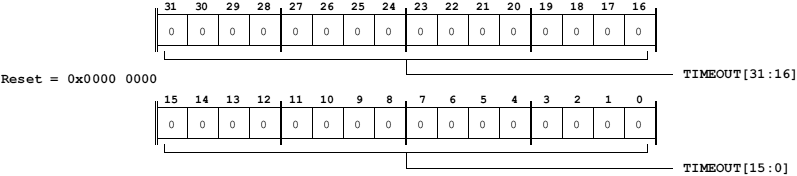

ąĀąĄą│ąĖčüčéčĆ RSI_DATA_TMR ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ, čćč鹊ą▒čŗ ąŠąĮ čĆą░ą▒ąŠčéą░ą╗ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆ čéą░ą╣ą╝ą░čāčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą░ąĮąĮčŗčģ (boot data timeout register). ąĢčüą╗ąĖ ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_CFG.BACKEN) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čĆąĄą│ąĖčüčéčĆ čéą░ą╣ą╝ą░čāčéą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (boot acknowledge timeout register, RSI_BACK_TOUT).

ąĀąĖčü. 24-7. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ Normal Boot Mode.

ąÜąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ RSI čĆą░ąĘčĆąĄčłąĄąĮą░ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ normal boot mode ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ RSI_CFG.MMCBEN, ą▓ ąŠą┤ąĮąŠą╝ čåąĖą║ą╗ąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ąĘą░ą┤ą░čćąĖ.

1. ąĪąĖą│ąĮą░ą╗ RSI_CMD ą┐čĆąĖčéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą║ ą╗ąŠą│. 0.

2. ąĀąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ boot setup (RSI_BOOT_TCNTR) ąĮą░čćąĖąĮą░ąĄčé čüą▓ąŠąĄ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĖąĄ.

3. ąĀąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ą░čāčéą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_BACK_TOUT) ąĮą░čćąĖąĮą░ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RSI_CFG.BACKEN.

4. ąĀąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ą░čāčéą░ ą┤ą░ąĮąĮčŗčģ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_DATA_TMR) ąĮą░čćąĖąĮą░ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ.

ąÜąŠą│ą┤ą░ ą┤ąĄą║čĆąĄą╝ąĄąĮčé čüč湥čéčćąĖą║ą░ boot setup ą┤ąŠą╣ą┤ąĄčé ą┤ąŠ ąĮčāą╗čÅ, ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖčüč鹥č湥ąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąĘą░ą│čĆčāąĘą║ąĖ (boot setup time expire), ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RSI_STAT0.BSETUPEXP. ąŁč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą║ą░čĆčéą░ ą▓ąŠčłą╗ą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ (boot state). ą×čćąĖčüčéą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ čéą░ą║ąČąĄ ąŠčćąĖčüčéąĖčé ąĖ čŹčéčā ą╗ąĖąĮąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čüąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ RSI_STAT0 ąĖą╝ąĄčÄčé čéąĖą┐ W1C (write-1-to-clear, čé. ąĄ. ą┤ą╗čÅ čüą▒čĆąŠčüą░ ą▒ąĖčéą░ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▓ ąĮąĄą│ąŠ ąĄą┤ąĖąĮąĖčåčā).

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_CFG.BACKEN), č鹊 RSI ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ ąŠąČąĖą┤ą░ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ, ą║ąŠč鹊čĆąŠąĄ ą┤ąŠą╗ąČąĮąŠ ą▓ąĄčĆąĮčāčéčī ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą▓čĆąĄą╝ąĄąĮąĖ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüč湥čéčćąĖą║ą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_BACK_TOUT). ąĢčüą╗ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé čŹč鹊ą╣ ą▓ąĄą╗ąĖčćąĖąĮčŗ, ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝čāčéą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé čéą░ą╣ą╝ą░čāčéą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_STAT0.BACKTO).

ąĢčüą╗ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊, ąĮąŠ ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ 010, č鹊 čéą░ą║ąČąĄ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_STAT0.BACKTO), ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ą┐čĆąĖąĄą╝ą░ ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (RSI_STAT0.BACKBAD).

ąÆ ąŠą▒ąŠąĖčģ čŹčéąĖčģ čüą╗čāčćą░čÅčģ RSI ą▓ąŠą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE. ą»ą┤čĆąŠ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄčĆą▓ą░čéčī čĆą░ą▒ąŠčéčā ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ RSI_CMD ą▓ ą╗ąŠą│. 1, čćč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ 0 ą▓ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ MMC (MMC boot enable bit, RSI_CFG.MMCBEN). ąóąĄą┐ąĄčĆčī ąĮą░čćąĮąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čāą┤ąĄčƹȹ░ąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (boot hold counter, RSI_BOOT_TCNTR). ąÜąŠą│ą┤ą░ čŹč鹊čé čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé 0, čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖčüč鹥č湥ąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (boot hold time expired interrupt), ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RSI_STAT0.BHOLDEXP. RSI ą╝ąŠąČąĄčé č鹥ą┐ąĄčĆčī ąĮą░čćą░čéčī ąŠą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĮąĄ čüą▓čÅąĘą░ąĮąĮąŠąĄ čü ąĘą░ą│čĆčāąĘą║ąŠą╣ (čģąŠčéčÅ čĆą░ą▒ąŠčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąĮąĄčāą┤ą░čćąĮąŠ).

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮą░ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ RSI_DATA_CTL, ąĄčüą╗ąĖ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ čüč湥čéčćąĖą║ RSI_BACK_TOUT, RSI ą▓ąŠą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT_R, ąĖ ą▒čāą┤ąĄčé ąŠąČąĖą┤ą░čéčī start-ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ.

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮą░ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ RSI_DATA_CTL, ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ ą▒ąĖčé RSI_CFG.BACKEN, č鹊 ąĮąĄ ą▒čāą┤ąĄčé ąŠąČąĖą┤ą░čéčīčüčÅ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ, ąĖ RSI ą▓ąŠą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ WAIT_R.

ą¤ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą┤ąŠą╣ą┤ąĄčé ą┤ąŠ ąĮčāą╗čÅ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ą░čāčéą░ ąĘą░ą│čĆčāąĘą║ąĖ (boot data timeout counter register, RSI_DATA_TMR). ąĢčüą╗ąĖ čŹč鹊čé čüč湥čéčćąĖą║ ą┤ąŠą╣ą┤ąĄčé ą┤ąŠ 0, ą║ąŠą│ą┤ą░ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čüąĄ ąĄčēąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ WAIT_R, č鹊 čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ą░čāčéą░ ą┤ą░ąĮąĮčŗčģ ąĘą░ą│čĆčāąĘą║ąĖ (boot data timeout interrupt), ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé RSI_STAT0.BDATTO. ą¤ąŠčüą╗ąĄ čéą░ą╣ą╝ą░čéčāą░ RSI ą▓ąŠą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

ąÜąŠą│ą┤ą░ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąĘą║ąĖ ą▒čŗą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ, čÅą┤čĆąŠ ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüą░čéčī 0 ą▓ ą▒ąĖčé RSI_CFG.MMCBEN, čćč鹊ą▒čŗ ą┐čĆąĄčĆčŗą▓ą░čéčī čĆą░ą▒ąŠčéčā čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ. ąĀąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čāą┤ąĄčƹȹ░ąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (boot hold counter RSI_BOOT_TCNTR) č鹥ą┐ąĄčĆčī ąĮą░čćąĮąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ, ąĖ ą║ąŠą│ą┤ą░ ąŠąĮ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĮčāą╗čÅ, čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖčüč鹥č湥ąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ (boot hold time expired interrupt), ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RSI_STAT0.BHOLDEXP. RSI ą╝ąŠąČąĄčé č鹥ą┐ąĄčĆčī ąĮą░čćą░čéčī ąŠą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĮąĄ čüą▓čÅąĘą░ąĮąĮąŠąĄ čü ąĘą░ą│čĆčāąĘą║ąŠą╣ (čģąŠčéčÅ čĆą░ą▒ąŠčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąĮąĄčāą┤ą░čćąĮąŠ).

ą¤ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ č鹥ą┐ąĄčĆčī ą│ąŠč鹊ą▓ąŠ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ CMD1. ąźąŠčüčé ą┤ąŠą╗ąČąĄąĮ ąĮą░čćą░čéčī ąŠą▒čŗčćąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ MMC ąŠčéą┐čĆą░ą▓ą║ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ CMD1.