|

ąØą░ ąŠčüąĮąŠą▓ąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ATmega ą╝ąŠąČąĮąŠ ą┤ąŠą▓ąŠą╗čīąĮąŠ ą┐čĆąŠčüč鹊 čüą┤ąĄą╗ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ. ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ąŠą┐ąĖčüą░ąĮ ą┐čĆąĖą╝ąĄčĆ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čéą░ą║ąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ ąĮą░ ąŠčüąĮąŠą▓ąĄ 16-ą▒ąĖčéąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 1, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą┤ąĄą╗ąĖčéčī čćą░čüč鹊čéčā ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ąŠčé 2 ą┤ąŠ 65535.

ąÆčŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ OC1A. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ ą▓čģąŠą┤ T1 (čŹč鹊 ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ CS12..CS10 čĆąĄą│ąĖčüčéčĆą░ TCCR1B, čüą╝. čéą░ą▒ą╗ąĖčåčā 19-6 ąĖąĘ čüčéą░čéčīąĖ [1]).

[ąØąĄč湥čéąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ]

ąöą╗čÅ ąĮąĄč湥čéąĮčŗčģ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ ą┤ąĄą╗ąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čĆąĄąČąĖą╝ Fast PWM 14 (ą▒ąĖčéčŗ WGM13..WGM10 čĆąĄą│ąĖčüčéčĆą░ TCCR1A čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 1110, čüą╝. čéą░ą▒ą╗ąĖčåčā 19-5 ąĖąĘ čüčéą░čéčīąĖ [1]). ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ą▓ąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ čüč湥čéą░ ąĘą░ą┤ą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ ICR1, ą░ ąĘąĮą░č湥ąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ąĘą░ą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ OCR1A. ąæąĖčéčŗ COM1A1 ąĖ COM1A0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 10, čćč鹊 ąĘą░ą┤ą░ąĄčé ąŠčćąĖčüčéą║čā čāčĆąŠą▓ąĮčÅ OC1A ą┐čĆąĖ Compare Match ąĖ čāčüčéą░ąĮąŠą▓ą║čā OC1A ąĮą░ BOTTOM (ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ čĆąĄąČąĖą╝).

ą¤čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ ą┤ąĄą╗ąĖč鹥ą╗čÅ čü ąĮąĄč湥čéąĮčŗą╝ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ą┤ąĄą╗ąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĖą╣. ąÆ čĆąĄą│ąĖčüčéčĆ ICR1 ąĘą░ą┐ąĖčüą░ąĮ ą┐čĆąĄą┤ąĄą╗ čüč湥čéą░ TOP [1], ą░ ą▓ čĆąĄą│ąĖčüčéčĆ OCR1A ą┐ąŠą╗ąŠą▓ąĖąĮą░ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ICR1. ąĪč湥čéčćąĖą║ ąĮą░čćąĖąĮą░ąĄčé čüč湥čé ąŠčé ąĮčāą╗čÅ (TCNT1==0), ą┐čĆąĖ čŹč鹊ą╝ ąĮą░ ą▓čŗčģąŠą┤ąĄ OC1A čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ TCNT1 ą┤ąŠčüčéąĖą│ą░ąĄčé ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ OCR1A, čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ OC1A ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0, ąĖ čüč湥čéčćąĖą║ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čüč湥čé. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ TCNT1 ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ICR1, č鹊 ąŠąĮ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0, ąĖ čāčĆąŠą▓ąĄąĮčī ąĮą░ OC1A ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąŠą▒čĆą░čéąĮąŠ ą▓ ą╗ąŠą│. 1. ąĪč湥čéčćąĖą║ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čüč湥čé ąŠčé ąĮčāą╗čÅ, ąĖ čåąĖą║ą╗ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 čćą░čüč鹊čéą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ OC1A ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą▓ (ICR1+1) čĆą░ąĘ ą╝ąĄąĮčīčłąĄ, č湥ą╝ čćą░čüč鹊čéą░, ą┐ąŠčüčéčāą┐ą░čÄčēą░čÅ ąĮą░ ą▓čģąŠą┤ T1. ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą║čāčüąŠą║ ą║ąŠą┤ą░, ąĮą░čüčéčĆą░ąĖą▓ą░čÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ 1 ąĮą░ ąĮąĄč湥čéąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ (ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ coeff):

/////////////////////////////////

// ąØąĄč湥čéąĮčŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ

//ąŚą░ą┐čĆąĄčéąĖčéčī čéą░ą╣ą╝ąĄčĆ 1:

TCCR1B &= ~((1 << CS12)|(1 << CS11)|(1 << CS10));

//ąĪą▒čĆąŠčü čüč湥čéčćąĖą║ą░ ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ:

TCNT1 = 0;

//ąĀąĄąČąĖą╝ 14 (ICR1==TOP, OC1A=0 ą┐čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ

// čü OCR1A, OC1A=1 ą┐čĆąĖ TOP):

ICR1 = coeff-1;

OCR1A = coeff >> 1;

TCCR1A = (1 << WGM11)|(1 << COM1A1);

TCCR1B = (1 << WGM13)|(1 << WGM12);

//ąĀą░ąĘčĆąĄčłąĖčéčī čéą░ą╣ą╝ąĄčĆčā 1 čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā T1:

TCCR1B |= ((1 << CS12)|(1 << CS11)|(1 << CS10));

[ą¦ąĄčéąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ]

ąŚą┤ąĄčüčī ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤čĆčāą│ąŠą╣ čĆąĄąČąĖą╝ Fast PWM 15 (ą▒ąĖčéčŗ WGM13..WGM10 čĆąĄą│ąĖčüčéčĆą░ TCCR1A čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 1111, čüą╝. čéą░ą▒ą╗ąĖčåčā 19-5 ąĖąĘ čüčéą░čéčīąĖ [1]). ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ą▓ąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ čüč湥čéą░ ąĘą░ą┤ą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ OCR1A. ąæąĖčéčŗ COM1A1 ąĖ COM1A0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 01, čćč鹊 ąĘą░ą┤ą░ąĄčé ąŠčćąĖčüčéą║čā ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ OC1A ą┐čĆąĖ Compare Match. ąó. ąĄ. ą┐čĆąĖ ą┤ąŠčüčéąĖąČąĄąĮąĖąĖ čüč湥čéčćąĖą║ąŠą╝ ąĘąĮą░č湥ąĮąĖčÅ OC1A čüč湥čéčćąĖą║ ąĮąĄ č鹊ą╗čīą║ąŠ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ąĮąŠ ąĖ ąĄčēąĄ čāčĆąŠą▓ąĄąĮčī ąĮą░ OC1A ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ ą▓čģąŠą┤ąĄ T1 ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ (2*OCR1A)+1. ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą║čāčüąŠą║ ą║ąŠą┤ą░, ąĮą░čüčéčĆą░ąĖą▓ą░čÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ 1 ąĮą░ č湥čéąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ (ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čéą░ą║ąČąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ coeff):

/////////////////////////////////

// ą¦ąĄčéąĮčŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ

//ąŚą░ą┐čĆąĄčéąĖčéčī čéą░ą╣ą╝ąĄčĆ 1:

TCCR1B &= ~((1 << CS12)|(1 << CS11)|(1 << CS10));

//ąĪą▒čĆąŠčü čüč湥čéčćąĖą║ą░, ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ:

TCNT1 = 0;

//ąĀąĄąČąĖą╝ 15 (OCR1A==TOP, OC1A ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą┐čĆąĖ TOP):

OCR1A = (coeff-1) >> 1;

TCCR1A = (1 << WGM11)|(1 << WGM10)|(1 << COM1A0);

TCCR1B = (1 << WGM13)|(1 << WGM12);

//ąĀą░ąĘčĆąĄčłąĖčéčī čéą░ą╣ą╝ąĄčĆčā 1 čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā T1:

TCCR1B |= ((1 << CS12)|(1 << CS11)|(1 << CS10));

ąóą░ą╣ą╝ąĄčĆ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ąŠčéą║ą╗čÄč湥ąĮąĖąĄą╝ ąĄą│ąŠ ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, čćč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ą▒ąĖčéčŗ CS12..CS10 ąĘąĮą░č湥ąĮąĖčÅ 000. ąŁč鹊 čüą┤ąĄą╗ą░ąĮąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą┐čāčüčéąĖčéčī čåąĖą║ą╗ čüč湥čéą░ ąŠčé ąĮčāą╗čÅ čüą▒čĆąŠčüąŠą╝ čüč湥čéčćąĖą║ą░ TCNT1. ąĢčüą╗ąĖ čŹč鹊ą│ąŠ ąĮąĄ čüą┤ąĄą╗ą░čéčī, č鹊 ąĮą░ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čéą░čģ, ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗčģ ąĮą░ ą▓čģąŠą┤ T1, ą▓ąŠąĘą╝ąŠąČąĮčŗ čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ čüč湥čéčćąĖą║ą░ ąŠą║ą░ąČąĄčéčüčÅ ą▒ąŠą╗čīčłąĄ ąĮąŠą▓čŗčģ ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖčģ ą┐čĆąĄą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéą░. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 čüč湥čéčćąĖą║ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čüčćąĖčéą░čéčī ą┤ąŠ ąĘąĮą░č湥ąĮąĖčÅ 65535, ą┐čĆąĄąČą┤ąĄ č湥ą╝ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ ą▓ 0 ąĖ ąĮą░čćąĮąĄčéčüčÅ ą┐čĆą░ą▓ąĖą╗čīąĮą░čÅ čĆą░ą▒ąŠčéą░ čüč湥čéčćąĖą║ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ.

[ą¤čĆą░ą║čéąĖč湥čüą║ąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ]

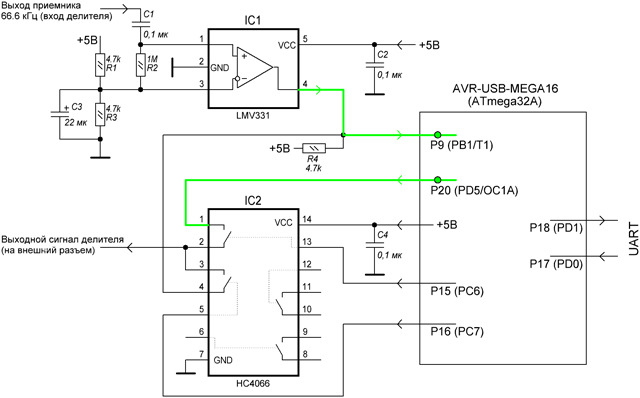

ą¤čĆąŠąĄą║čé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ ą║ą░ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čŹčéą░ą╗ąŠąĮąĮąŠą╣ čćą░čüč鹊čéčŗ čü ą▓čŗčģąŠą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ 66.6(6) ą║ąōčå [3]. ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čüčģąĄą╝ą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ. ąŚąĄą╗ąĄąĮčŗą╝ąĖ ą╗ąĖąĮąĖčÅą╝ąĖ ą┐ąŠą║ą░ąĘą░ąĮčŗ čüąĖą│ąĮą░ą╗čŗ ąĮą░ ą▓čģąŠą┤ąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ (PB1/T1) ąĖ ąĮą░ ąĄą│ąŠ ą▓čŗčģąŠą┤ąĄ (PD5/OC1A).

ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ LMV331 ąĮčāąČąĄąĮ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čü ą▓čŗčģąŠą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▓ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą░čéčī ąĮą░ ą▓čģąŠą┤ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ T1 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ PB1 ATmega32A). ąÜąŠą╝ą╝čāčéą░č鹊čĆ ąĮą░ HC4066 ąĮčāąČąĄąĮ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ ą▓čŗčģąŠą┤ ą╗ąĖą▒ąŠ čüąĖą│ąĮą░ą╗ą░ čü ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░, ą╗ąĖą▒ąŠ čü ą▓čŗčģąŠą┤ą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ OC1A (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ PD5 ATmega32A). ąÜą╗čÄčćąĖ HC4066 čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (PC6 ąĖ PC7 ATmega32A). ą¦ąĄčĆąĄąĘ ą┐ąŠčĆčé UART (PD0 ATmega32A) ą┐ąŠą┤ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 65535.

Makefile-ą┐čĆąŠąĄą║čé ATmega-freq-divider čü ąĖčüčģąŠą┤ąĮčŗą╝ ą║ąŠą┤ąŠą╝ ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ATmega32 (ą┐čĆąŠąĄą║čé ą║ąŠą╝ą┐ąĖą╗ąĖčĆčāąĄčéčüčÅ ąĖ ą┤ą╗čÅ ATmega16) ą╝ąŠąČąĮąŠ čüą║ą░čćą░čéčī ą┐ąŠ čüčüčŗą╗ą║ąĄ [2]. ąĪ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅą╝ąĖ ą┐čĆąŠąĄą║čé ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮą░ ą╗čÄą▒ąŠą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ATmega/AVR, ą│ą┤ąĄ ąĮą░ ą▒ąŠčĆčéčā ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ čü ą▓ąĮąĄčłąĮąĖą╝ ą▓čģąŠą┤ąŠą╝ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ čéą░ą║č鹊ą▓ Tx (T0, T1, ąĖ čé. ą┤. ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░).

[ąĪčüčŗą╗ą║ąĖ]

1. ATmega32: 16-ą▒ąĖčéąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ 1.

2. 180909ATmega-freq-divider.zip - ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ čüč湥čéčćąĖą║ą░-ą┤ąĄą╗ąĖč鹥ą╗čÅ (makefile-ą┐čĆąŠąĄą║čé ą┤ą╗čÅ Visual Studio 2010, ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ).

3. ąøčÄą▒ąĖč鹥ą╗čīčüą║ąĖą╣ ą┐čĆąĖąĄą╝ąĮąĖą║ čŹčéą░ą╗ąŠąĮąĮąŠą╣ čćą░čüč鹊čéčŗ. |