|

ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą╝ą░č鹥čĆąĖą░ą╗ąŠą▓ ą┤ą░čéą░čłąĖčéą░, ą║ą░čüą░čÄčēąĖčģčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ ąĖ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ OneWire EEPROM DS2431. ąśąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝, ąĘąĮą░č湥ąĮąĖčÅą╝ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠčĆą┐čāčüčā čüą╝. ą▓ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą╝ ą┤ą░čéą░čłąĖč鹥 ąĮą░ DS2431 [1].

DS2431 ą║ąŠą╝ą▒ąĖąĮąĖčĆčāąĄčé ą▓ąĮčāčéčĆąĖ čüąĄą▒čÅ 1024 ą▒ąĖčéą░ EEPROM, 8-ą▒ą░ą╣čéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ/čüčéčĆą░ąĮąĖčåą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ą│ą┤ąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ 7 ą▒ą░ą╣čé, ąĖ ą┐ąŠą╗ąĮąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü 1-Wire. ąÆ ą║ą░ąČą┤ąŠą╝ čćąĖą┐ąĄ DS2431 ąĄčüčéčī čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ 64-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ąĮąĄ čüčéąĖčĆą░ąĄą╝čŗą╣ čüąĄčĆąĖą╣ąĮčŗą╣ ąĮąŠą╝ąĄčĆ (ROM registration number, ąĖą╗ąĖ 64-bit lasered ROM), ą┐čĆąŠčłąĖčéčŗą╣ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ ą┐čĆąĖ ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮąĖąĖ. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą║ą░ąČą┤čŗą╣ čćąĖą┐ ą╝ąŠąČąĄčé ą▒čŗčéčī ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ. ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąŠ ą┐čĆąŠč鹊ą║ąŠą╗čā 1-Wire, ą║ąŠč鹊čĆčŗą╣ čéčĆąĄą▒čāąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗čīąĮąŠą│ąŠ ą┐čĆąŠą▓ąŠą┤ą░ ąĖ ąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠą▓ąŠą┤ą░ ąĘąĄą╝ą╗ąĖ. ąŻ DS2431 ąĄčüčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ scratchpad, ąĖ ąŠąĮą░ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▒čāč乥čĆ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ čüčéčĆą░ąĮąĖčåčŗ čĆąĄą│ąĖčüčéčĆą░. ąöą░ąĮąĮčŗąĄ čüąĮą░čćą░ą╗ą░ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ scratchpad, ąŠčéą║čāą┤ą░ ąĖčģ ą┐ąŠč鹊ą╝ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ąŠą▒čĆą░čéąĮąŠ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąŠą▓ąĄčĆąĄąĮčŗ, ą║ąŠą╝ą░ąĮą┤ą░ Copy Scratchpad ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ čüą▓ąŠąĄ ą║ąŠąĮąĄčćąĮąŠąĄ ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą┐ą░ą╝čÅčéąĖ. ą×ą▒ą╗ą░čüčéąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ DS2431 ą▓ą║ą╗čÄčćą░čÄčé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ ąĖąĘą┤ąĄą╗ąĖą╣/PCB, ą╝ąĄą┤ąĖčåąĖąĮčüą║ąĖąĄ ą┤ą░čéčćąĖą║ąĖ, ą▓ ą║ąŠč鹊čĆčŗčģ čģčĆą░ąĮčÅčéčüčÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ąŠčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ (ą▓ą║ą╗čÄčćą░čÅ smart- čüąĄąĮčüąŠčĆčŗ IEEE P1451.4), ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ ą║ą░čĆčéčĆąĖą┤ąČąĄą╣ č湥čĆąĮąĖą╗ ąĖ č鹊ąĮąĄčĆą░ ąĖ čé. ą┐.

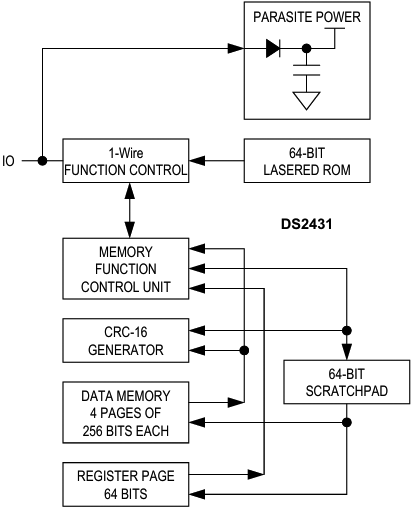

ąØą░ ą▒ą╗ąŠą║-čüčģąĄą╝ąĄ čĆąĖčü. 1 ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠą▒čēą░čÅ ą▓ąĘą░ąĖą╝ąŠčüą▓čÅąĘčī ą╝ąĄąČą┤čā ąŠčüąĮąŠą▓ąĮčŗą╝ąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╝ąĖ čāąĘą╗ą░ą╝ąĖ DS2431. DS2431 čüąŠą┤ąĄčƹȹĖčé 4 ąŠčüąĮąŠą▓ąĮčŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ:

- 64-bit lasered ROM

- 64-bit scratchpad

- 4 čüčéčĆą░ąĮąĖčåčŗ ą┐ąŠ 32 ą▒ą░ą╣čéą░

- 64-čĆą░ąĘčĆčÅą┤ąĮą░čÅ čüčéčĆą░ąĮąĖčåą░ čĆąĄą│ąĖčüčéčĆą░.

ąĀąĖčü. 1. ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čüčéčĆčāą║čéčāčĆą░ DS2431.

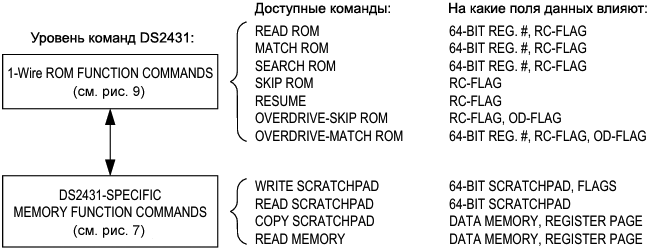

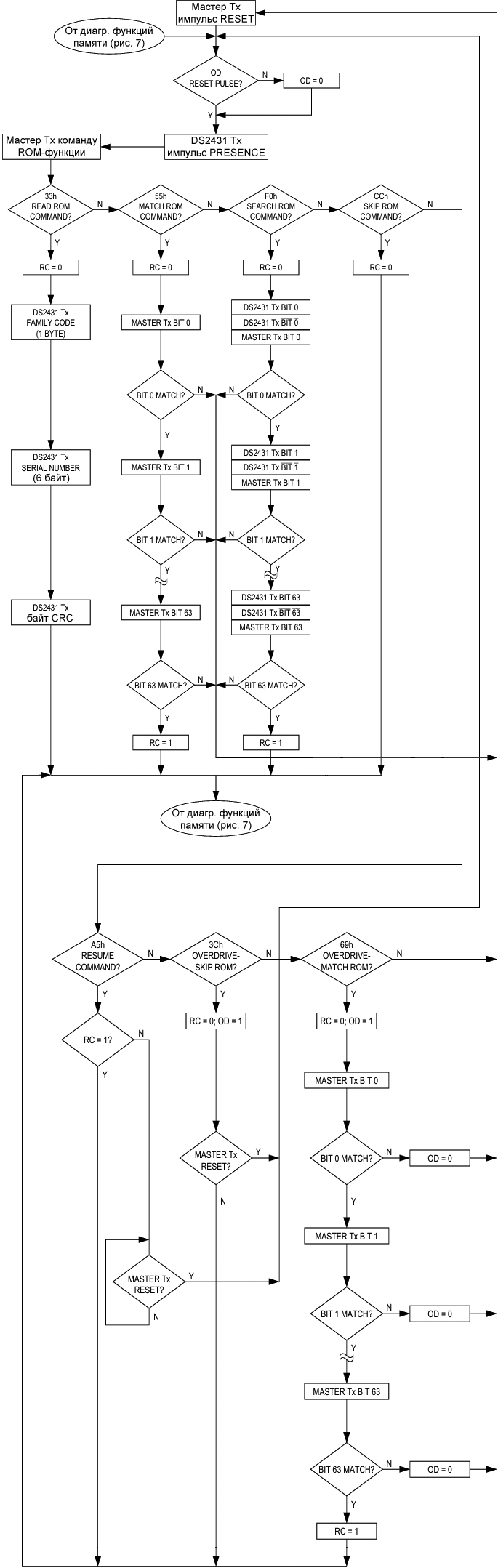

ąśąĄčĆą░čĆčģąĖč湥čüą║ą░čÅ čüčéčĆčāą║čéčāčĆą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ 1-Wire ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 2. ą£ą░čüč鹥čĆ čłąĖąĮčŗ ą┤ąŠą╗ąČąĄąĮ čüąĮą░čćą░ą╗ą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ąŠą┤ąĮčā ąĖąĘ 7 čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ ROM: Read ROM, Match ROM, Search ROM, Skip ROM, Resume, Overdrive-Skip ROM ąĖą╗ąĖ Overdrive-Match ROM. ą¤čĆąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą║ąŠą╝ą░ąĮą┤čŗ Overdrive-Skip ROM ąĖą╗ąĖ Overdrive-Match ROM, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĮąŠą╣ ąĮą░ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ overdrive, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ. ą¤čĆąŠč鹊ą║ąŠą╗, čéčĆąĄą▒čāąĄą╝čŗą╣ ą┤ą╗čÅ čŹčéąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ ROM, ąŠą┐ąĖčüą░ąĮ ąĮą░ čĆąĖčü. 9.

ąĀąĖčü. 2. ąśąĄčĆą░čĆčģąĖč湥čüą║ą░čÅ čüčéčĆčāą║čéčāčĆą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ 1-Wire.

ąĀąĖčü. 3. 64-ą▒ąĖčé Lasered ROM.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ROM čāčüą┐ąĄčłąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░, čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┤ąŠčüčéčāą┐ąĮčŗ čäčāąĮą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ, ąĖ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą╝ąŠąČąĄčé ą▓čŗą┤ą░čéčī ąŠą┤ąĮčā ąĖąĘ 4 ą║ąŠą╝ą░ąĮą┤ čäčāąĮą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ. ą¤čĆąŠč鹊ą║ąŠą╗ čŹčéąĖčģ ą║ąŠą╝ą░ąĮą┤ ąŠą┐ąĖčüą░ąĮ ąĮą░ čĆąĖčü. 7. ąÆčüąĄ ą┤ą░ąĮąĮčŗąĄ čćąĖčéą░čÄčéčüčÅ ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ (least significant bit, LSB) ą▓ą┐ąĄčĆąĄą┤.

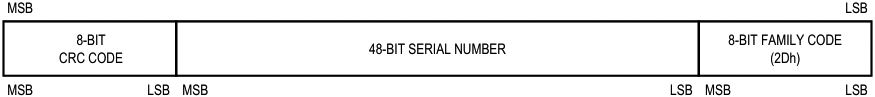

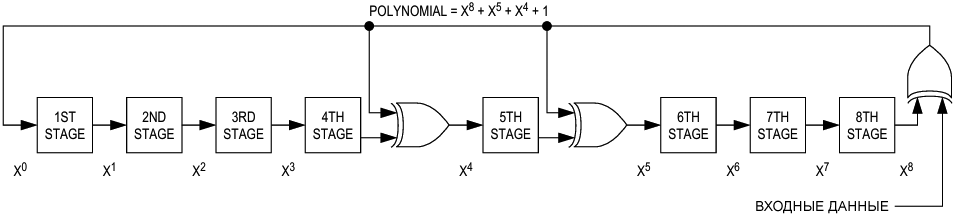

64-ą▒ąĖčé Lasered ROM. ąÜą░ąČą┤ą░čÅ DS2431 čüąŠą┤ąĄčƹȹĖčé čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ROM-ą║ąŠą┤ čĆą░ąĘą╝ąĄčĆąŠą╝ 64 ą▒ąĖčéą░. ą¤ąĄčĆą▓čŗąĄ 8 ą▒ąĖčé čŹč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą║ąŠą┤ čüąĄą╝ąĄą╣čüčéą▓ą░ (1-Wire family code), čé. ąĄ. ą║ąŠą┤, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮą░ąĘąĮą░č湥ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ (ą┤ą╗čÅ DS2431 ąŠąĮ čĆą░ą▓ąĄąĮ 0x2D, ąĖą╗ąĖ 45 ą┤ąĄčüčÅčéąĖčćąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ). ąĪą╗ąĄą┤čāčÄčēąĖąĄ 48 ą▒ąĖčé ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüąŠą▒ąŠą╣ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ čüąĄčĆąĖą╣ąĮčŗą╣ ąĮąŠą╝ąĄčĆ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąŠčüą╗ąĄą┤ąĮąĖąĄ 8 čŹč鹊 ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ (CRC) ąŠčé ą┐ąĄčĆą▓čŗčģ 56 ą▒ąĖčé, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆąĖčü. 3. 1-Wire CRC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąĖąĮąŠą╝ąĮčŗą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝, čüąŠčüč鹊čÅčēąĖą╝ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĖ ą╗ąŠą│ąĖč湥čüą║ąĖčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓ XOR, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╝ ąĮą░ čĆąĖčü. 4. ą¤ąŠą╗ąĖąĮąŠą╝ čŹč鹊ą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ X8 + X5 + X4 + 1. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ 1-Wire CRC ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąĖąĘ ą░ą┐ąĮąŠčāčéą░ [2].

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ąĮčāą╗čÅą╝ąĖ. ąŚą░č鹥ą╝, ąĮą░čćąĖąĮą░čÅ čü čüą░ą╝ąŠą│ąŠ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ąĖčéą░ family code, ą▒ąĖčéčŗ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą▓ čĆąĄą│ąĖčüčéčĆ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ 8-ą╣ ą▒ąĖčé family code ą▒čŗą╗ ą▓ą▓ąĄą┤ąĄąĮ, ą┤ą▓ąĖą│ą░ąĄčéčüčÅ čüąĄčĆąĖą╣ąĮčŗą╣ ąĮąŠą╝ąĄčĆ. ą¤ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ąĖčéą░ čüąĄčĆąĖą╣ąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ CRC. ąĢčüą╗ąĖ ą▓ą┤ą▓ąĖąĮčāčéčī ą▓ čĆąĄą│ąĖčüčéčĆ 8 ą▒ąĖčé ą║ąŠą┤ą░ CRC, č鹊 ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ąŠą║ą░ąČčāčéčüčÅ ą▓čüąĄ ąĮčāą╗ąĖ.

ąĀąĖčü. 4. ąōąĄąĮąĄčĆą░č鹊čĆ 1-Wire CRC.

[ąöąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ]

ą¤ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ ąĖ čĆąĄą│ąĖčüčéčĆčŗ čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ ą╗ąĖąĮąĄą╣ąĮąŠą╝ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 5. ą¤ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ ąĖ čĆąĄą│ąĖčüčéčĆčŗ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ąĮąĄąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ. ą£ą░čüčüąĖą▓ DS2431 EEPROM ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ 18 čüčéčĆąŠą║ ą┐ąŠ 8 ą▒ą░ą╣čé ą║ą░ąČą┤ą░čÅ. ą¤ąĄčĆą▓čŗąĄ 16 čüčéčĆąŠą║ ą┐ąŠą┤ąĄą╗ąĄąĮčŗ ąĮą░ 4 ąŠą┤ąĖąĮą░ą║ąŠą▓čŗčģ ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ (ą║ą░ąČą┤ą░čÅ ą┐ąŠ 32 ą▒ą░ą╣čéą░). ąŁčéąĖ 4 čüčéčĆą░ąĮąĖčåčŗ čüąŠčüčéą░ą▓ą╗čÅčÄčé ąŠčüąĮąŠą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ. ąÜą░ąČą┤ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąĮą░ ąŠčéą║čĆčŗčéąĖąĄ (ąĮąĄ ąĘą░čēąĖčēąĄąĮąĮąŠą╣), ąĘą░čēąĖčēąĄąĮąĮąŠą╣ ąŠčé ąĘą░ą┐ąĖčüąĖ, ąĖą╗ąĖ čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ EPROM ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ą░ą╣čéą░ ąĘą░čēąĖčéčŗ ą▓ čüčéčĆąŠą║ąĄ čĆąĄą│ąĖčüčéčĆą░. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĘą░ą▓ąŠą┤čüą║ąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ąŠčüčéą░ą▓ą╗čÅčÄčé ąĮąĄąĘą░čēąĖčēąĄąĮąĮąŠą╣ ą▓čüčÄ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ, ąĖ ąĄčæ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą▒čŗą╗ą░ čü ąĘą░ą▓ąŠą┤ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮą░ ą▒ą░ą╣čéą░ą╝ąĖ 0x00). ą¤ąŠčüą╗ąĄą┤ąĮąĖąĄ 2 čüčéčĆąŠą║ąĖ čüąŠą┤ąĄčƹȹ░čé čĆąĄą│ąĖčüčéčĆčŗ ąĘą░čēąĖčéčŗ (protection registers) ąĖ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▒ą░ą╣čéčŗ. ąĪčéčĆąŠą║ą░ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊ąĖčé ąĖąĘ 4 čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ąĘą░čēąĖč鹊ą╣ ą▒ą░ą╣č鹊ą▓ (protection control bytes), ą▒ą░ą╣čéą░ ąĘą░čēąĖčéčŗ ąŠčé ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ, factory byte, ąĖ 2 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖčģ ą▒ą░ą╣čéą░ (byte/manufacture ID). Manufacturer ID ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗą╝ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╝ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąŠąĮąĮčŗą╝ ą║ąŠą┤ąŠą╝ (custom manufacturer ID), ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą╝ąŠą│ą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą┐čĆąŠą┤čāą║čé, čü ą║ąŠč鹊čĆčŗą╝ čüą▓čÅąĘą░ąĮ čćąĖą┐ DS2431.

| ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÜąŠą┤čŗ ąĘą░čēąĖčéčŗ |

| 0000h .. 001Fh |

R/(W) |

Data Memory Page 0 |

- |

| 0020h .. 003Fh |

R/(W) |

Data Memory Page 1 |

- |

| 0040h .. 005Fh |

R/(W) |

Data Memory Page 2 |

- |

| 0060h .. 007Fh |

R/(W) |

Data Memory Page 3 |

- |

| 0080h* |

R/(W) |

Protection Control Byte Page 0 |

55h: Write Protect P0; AAh: EPROM Mode P0;

55h ąĖą╗ąĖ AAh: Write Protect 80h |

| 0081h* |

R/(W) |

Protection Control Byte Page 1 |

55h: Write Protect P1; AAh: EPROM Mode P1;

55h ąĖą╗ąĖ AAh: Write Protect 81h |

| 0082h* |

R/(W) |

Protection Control Byte Page 2 |

55h: Write Protect P2; AAh: EPROM Mode P2;

55h ąĖą╗ąĖ AAh: Write Protect 82h |

| 0083h* |

R/(W) |

Protection Control Byte Page 3 |

55h: Write Protect P3; AAh: EPROM Mode P3;

55h ąĖą╗ąĖ AAh: Write Protect 83h |

| 0084h* |

R/(W) |

Copy Protection Byte |

55h ąĖą╗ąĖ AAh: Copy Protect 0080h:008Fh,

ąĖ ą╗čÄą▒čŗąĄ ąĘą░čēąĖčēąĄąĮąĮčŗąĄ ąŠčé ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ |

| 0085h |

R |

Factory Byte. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ. |

AAh: Write Protect 85h, 86h, 87h; 55h: Write Protect 85h;

ąŠčéą╝ąĄąĮą░ ąĘą░čēąĖčéčŗ 86h, 87h |

| 0086h |

R/(W) |

User Byte/Manufacturer ID |

- |

| 0087h |

R/(W) |

User Byte/Manufacturer ID |

- |

| 0088h .. 008Fh |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

ąĀąĖčü. 5. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ DS2431.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: ą▒čāą┤čāčćąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą▓ AAh ąĖą╗ąĖ 55h čŹč鹊čé ą░ą┤čĆąĄčü čüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ąÆčüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą║ąŠą┤čŗ ą╝ąŠąČąĮąŠ čüąŠčģčĆą░ąĮąĖčéčī, ąĮąŠ ąŠąĮąĖ ąĮąĄ ąĘą░čēąĖčēą░čÄčé ą░ą┤čĆąĄčü ąŠčé ąĘą░ą┐ąĖčüąĖ ąĖ ąĮąĄ ą░ą║čéąĖą▓ąĖčĆčāčÄčé ąĮąĖą║ą░ą║ąĖčģ čäčāąĮą║čåąĖą╣.

ąĪą▓čÅąČąĖč鹥čüčī čü ąĘą░ą▓ąŠą┤ąŠą╝ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ čĆąĄą│ąĖčüčéčĆą░čåąĖąĖ custom manufacturer ID. ą¤ąŠčüą╗ąĄą┤ąĮčÅčÅ čüčéčĆąŠą║ą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮą░ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą▒čāą┤čāčēąĄą╝. ą×ąĮą░ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą▓ ą║ąŠąĮč鹥ą║čüč鹥 čäčāąĮą║čåąĖąŠąĮą░ą╗ą░ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (R/W) ąĖ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ.

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ąŠčüąĮąŠą▓ąĮąŠą╝čā ą╝ą░čüčüąĖą▓čā ą┐ą░ą╝čÅčéąĖ EEPROM ąĖą╝ąĄąĄčéčüčÅ 8-ą▒ą░ą╣čéąĮčŗą╣ ą▒čāč乥čĆ (volatile scratchpad). ąŚą░ą┐ąĖčüčī ą▓ ą╝ą░čüčüąĖą▓ EEPROM čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐čĆąŠčåąĄčüčü ąĖąĘ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ 2 čłą░ą│ąŠą▓. ąĪąĮą░čćą░ą╗ą░ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ scratchpad, ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą╝ą░čüčüąĖą▓. ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čüąĮą░čćą░ą╗ą░ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą┤ą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ scratchpad, ą┐ąĄčĆąĄą┤ ąĖčģ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą╝ą░čüčüąĖą▓. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č鹊ą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖąĖ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠą╗ąĮąŠą╣ čüčéčĆąŠą║ąĖ (8 ą▒ą░ą╣čé). ą¦č鹊ą▒čŗ ą┤ą░ąĮąĮčŗąĄ ą▓ scratchpad ą▒čŗą╗ąĖ ą┤ąŠą┐čāčüčéąĖą╝čŗ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ ą║ąŠą╝ą░ąĮą┤čŗ Write Scratchpad ą┤ąŠą╗ąČąĄąĮ ąĮą░čćąĖąĮą░čéčīčüčÅ ąĮą░ ą│čĆą░ąĮąĖčåąĄ čüčéčĆąŠą║ąĖ (čé. ąĄ. ą┤ąŠą╗ąČąĄąĮ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 8), ąĖ ą▓čüąĄ 8 ą▒ą░ą╣čé ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ scratchpad.

ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čēąĖč鹊ą╣ (protection control registers) ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą║ąŠą╝ą░ąĮą┤ąĄ Write Scratchpad ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ scratchpad. ąŚą░čēąĖčéą░, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮą░čÅ ą▓ 55h (write protect) ąĘą░čüčéą░ą▓ą╗čÅąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĖ čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, čéą░ą║ čćč鹊 ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ scratchpad ąĖ ąŠčüąĮąŠą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī. ąŚą░čēąĖčéą░, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮą░čÅ ą▓ AAh (čĆąĄąČąĖą╝ EPROM), ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ ąś (AND) ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ, ąĮą░čģąŠą┤čÅčēąĖą╝ąĖčüčÅ ą┐ąŠ čåąĄą╗ąĄą▓ąŠą╝čā ą░ą┤čĆąĄčüčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąĖ čĆąĄąĘčāą╗čīčéą░čé čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ scratchpad. ąøčÄą▒ąŠąĄ ą┤čĆčāą│ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čēąĖč鹊ą╣ ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąĄąĘą░čēąĖčēąĄąĮąĮąŠą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ čüčéčĆą░ąĮąĖčåčā ą┐ą░ą╝čÅčéąĖ, ą┤ą░ą▓ą░čÅ ą║ ąĮąĄą╣ ąĮąĄąŠą│čĆą░ąĮąĖč湥ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī. ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čĆąĄąČąĖą╝ąŠą╝ EPROM, ą▓čüąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ FFh. ąØą░čüčéčĆąŠą╣ą║ą░ ą▒ą░ą╣čéą░ ąĘą░čēąĖčéčŗ (protection-control byte) 55h ąĖą╗ąĖ AAh čéą░ą║ąČąĄ ąĘą░čēąĖčēą░ąĄčé ąĖ ąĄą│ąŠ čüą░ą╝ąŠą│ąŠ. ąØą░čüčéčĆąŠą╣ą║ą░ protection-control byte 55h ąĮąĄ ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą▒ąĮąŠą▓ą╗čÅčéčī ąĘą░čēąĖčēąĄąĮąĮčŗąĄ ąŠčé ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗąĄ (čé.ąĄ. ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĖčģ č鹥ą║čāčēąĖą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ) ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ.

ąæą░ą╣čé ąĘą░čēąĖčéčŗ ąŠčé ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ (copy-protection byte) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĘą░čēąĖčéčŗ, ąĖ ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▓čüąĄ ą┤čĆčāą│ąĖąĄ ą▒ą░ą╣čéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čēąĖč鹊ą╣, ą▒ą░ą╣čéčŗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĖ ąĘą░čēąĖčēąĄąĮąĮčŗąĄ ąŠčé ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čüą▓ąŠčæ ą║ąŠąĮąĄčćąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąĢčüą╗ąĖ copy-protection byte čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 55h ąĖą╗ąĖ AAh, č鹊 ą▓čüąĄ ą┐ąŠą┐čŗčéą║ąĖ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ čüčéčĆąŠą║čā čĆąĄą│ąĖčüčéčĆą░ ąĖ čüčéčĆąŠą║čā ą▒ą░ą╣čé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▒ą╗ąŠą║ąĖčĆčāčÄčéčüčÅ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą▒ą╗ąŠą║ąĖčĆčāčÄčéčüčÅ ą▓čüąĄ ą┐ąŠą┐čŗčéą║ąĖ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░čēąĖčēąĄąĮąĮčŗčģ ąŠčé ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčå ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (čé. ąĄ. ąĖčģ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ).

ąĀąĄą│ąĖčüčéčĆčŗ ą░ą┤čĆąĄčüą░ ąĖ čüčéą░čéčāčü čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąÆ DS2431 ąĄčüčéčī 3 čĆąĄą│ąĖčüčéčĆą░ ą░ą┤čĆąĄčüą░: TA1, TA2 ąĖ E/S (čĆąĖčü. 6). ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ čéą░ą║ąČąĄ ąĄčüčéčī ą▓ąŠ ą╝ąĮąŠą│ąĖčģ ą┤čĆčāą│ąĖčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ 1-Wire, ąĮąŠ čā DS2431 ąŠąĮąĖ čĆą░ą▒ąŠčéą░čÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠ-ą┤čĆčāą│ąŠą╝čā. ąĀąĄą│ąĖčüčéčĆčŗ TA1 ąĖ TA2 ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ čåąĄą╗ąĄą▓čŗą╝ ą░ą┤čĆąĄčüąŠą╝ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā ą┤ą░ąĮąĮčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ąĖą╗ąĖ čüčćąĖčéą░ąĮčŗ. ąĀąĄą│ąĖčüčéčĆ E/S čŹč鹊 čĆąĄą│ąĖčüčéčĆ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ą▓ ą║ąŠč鹊čĆąŠą╝ ą┤ąŠčüčéčāą┐ąĮą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠ čüąŠčüč鹊čÅąĮąĖąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ą┐ąŠ ą║ąŠč鹊čĆąŠą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą▓ ą║ąŠą╝ą░ąĮą┤ą░čģ ąĘą░ą┐ąĖčüąĖ. ąæąĖčéčŗ E[2:0] čĆąĄą│ąĖčüčéčĆą░ E/S ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą┐čĆąĖčģąŠą┤čÅčēąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ T[2:0] ąĮą░ ą║ąŠą╝ą░ąĮą┤ąĄ Write Scratchpad, ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāčÄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╝ ą▒ą░ą╣č鹥 ą┤ą░ąĮąĮčŗčģ. ą¤ąŠ čüčāčéąĖ čŹč鹊 čüč湥čéčćąĖą║ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ąĘą░ą┐ąĖčüą░ąĮąĮąŠą│ąŠ ą▒ą░ą╣čéą░ ą▓ 8-ą▒ą░ą╣čéąĮąŠą╝ scratchpad. ąæąĖčé 5 čĆąĄą│ąĖčüčéčĆą░ E/S, ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ PF, čüąŠą┤ąĄčƹȹĖčé ą╗ąŠą│. 1, ąĄčüą╗ąĖ ą┤ą░ąĮąĮčŗąĄ ą▓ scratchpad ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗ ąĖąĘ-ąĘą░ ą┐ąŠč鹥čĆąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╗ąĖ ąĄčüą╗ąĖ master ą┐ąŠčüą╗ą░ą╗ ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠąĄ ą┤ą╗čÅ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą║ąŠąĮčåą░ scratchpad. ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ scratchpad ą▒čŗą╗ ą┤ąŠą┐čāčüčéąĖą╝ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ, ą▒ąĖčéčŗ T[2:0] ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī 0, ąĖ ą┤ą╗čÅ čŹč鹊ą│ąŠ master ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčüą╗ą░čéčī 8 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ. ąæąĖčéčŗ 3, 4, ąĖ 6 ąĮąĄ ąŠą▒čĆąĄą╝ąĄąĮąĄąĮčŗ ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ čäčāąĮą║čåąĖąĄą╣, ąŠąĮąĖ ą▓čüąĄą│ą┤ą░ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ 0. ąĪą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ E/S ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ authorization accepted (AA), ąŠąĮ ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ čäą╗ą░ą│ ą┤ą╗čÅ ąĖąĮą┤ąĖą║ą░čåąĖąĖ, čćč鹊 ą┤ą░ąĮąĮčŗąĄ, čüą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▓ scratchpad, ą▒čŗą╗ąĖ čāąČąĄ čüą║ąŠą┐ąĖčĆąŠą▓ą░ąĮčŗ ą┐ąŠ čåąĄą╗ąĄą▓ąŠą╝čā ą░ą┤čĆąĄčüčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąŚą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ ą▓ scratchpad ąŠčćąĖčēą░ąĄčé čŹč鹊čé čäą╗ą░ą│.

| Ōä¢ ą▒ąĖčéą░ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TARGET ADDRESS (TA1) |

T7 |

T6 |

T5 |

T4 |

T3 |

T2 |

T1 |

T0 |

| TARGET ADDRESS (TA2) |

T15 |

T14 |

T13 |

T12 |

T11 |

T10 |

T9 |

T8 |

| ąÜąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü čüąŠ čüčéą░čéčāčüąŠą╝ ą┤ą░ąĮąĮčŗčģ (E/S, č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ) |

AA |

0 |

PF |

0 |

0 |

E2 |

E1 |

E0 |

ąĀąĖčü. 6. ąĀąĄą│ąĖčüčéčĆčŗ ą░ą┤čĆąĄčüą░.

ąŚą░ą┐ąĖčüčī čü ą▓ąĄčĆąĖčäąĖą║ą░čåąĖąĄą╣. ą¦č鹊ą▒čŗ ąĘą░ą┐ąĖčüą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ DS2431, ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ scratchpad ą║ą░ą║ ą┐čĆąŠą╝ąĄąČčāč鹊čćąĮąŠąĄ čģčĆą░ąĮąĖą╗ąĖčēąĄ. ąĪąĮą░čćą░ą╗ą░ master ą▓čŗą┤ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā Write Scratchpad, čćč鹊ą▒čŗ čāą║ą░ąĘą░čéčī ąČąĄą╗ą░ąĄą╝čŗą╣ čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ąĘą░ą┐ąĖčüąĖ, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤čāčé ą┤ą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą▓ scratchpad. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ąŠą╝ą░ąĮą┤ą░ Copy Scratchpad ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĮą░ 8-ą▒ą░ą╣čéąĮčŗčģ ą│čĆą░ąĮąĖčåą░čģ, čé. ąĄ. ą╝ą╗ą░ą┤čłąĖąĄ 3 ą▒ąĖčéą░ čåąĄą╗ąĄą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ (T2, T1, T0) ą┤ąŠą╗ąČąĮčŗ čĆą░ą▓ąĮčÅčéčīčüčÅ 000b (čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 8). ąĢčüą╗ąĖ T[2:0] ą▒čŗą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ čā ąĮąĄąĮčāą╗ąĄą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, č鹊 čäčāąĮą║čåąĖčÅ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ ąŠčüąĮąŠą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ. ąÆ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čāčüą╗ąŠą▓ąĖčÅčģ (čüą╝. čüąĄą║čåąĖčÄ "Write Scratchpad [0Fh]") master ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮčāčÄ CRC-16 ą║ąŠą╝ą░ąĮą┤čŗ, ą░ą┤čĆąĄčü (čäą░ą║čéąĖč湥čüą║ąĖą╣ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü) ąĖ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą║ąŠą╝ą░ąĮą┤čŗ Write Scratchpad. ąŚąĮą░čÅ čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ CRC, master ą╝ąŠąČąĄčé ąĄą│ąŠ čüčĆą░ą▓ąĮąĖčéčī čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝, ą║ąŠč鹊čĆčŗą╣ ąŠąĮ čüą░ą╝ ą▓čŗčćąĖčüą╗ąĖą╗, čćč鹊ą▒čŗ čāą┤ąŠčüč鹊ą▓ąĄčĆąĖčéčīčüčÅ, čćč鹊 ąŠą▒ą╝ąĄąĮ ą▒čŗą╗ čüąŠą▓ąĄčĆčłąĄąĮ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą╝ąŠąČąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤ą░ Copy Scratchpad. ąĢčüą╗ąĖ master ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī CRC-16, č鹊 ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčüą╗ą░čéčī ą║ąŠą╝ą░ąĮą┤čā Read Scratchpad, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ. ąÜą░ą║ ą┐čĆąĄą░ą╝ą▒čāą╗ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ scratchpad, DS2431 ą┐ąŠą▓č鹊čĆčÅąĄčé čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü TA1 ąĖ TA2, ąĖ ą┐ąŠčüčŗą╗ą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ E/S. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ PF, č鹊 ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┤ąŠčüčéąĖą│ą╗ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠ scratchpad, ąĖą╗ąĖ ą▒čŗą╗ąŠ ą┐čĆąŠą┐ą░ą┤ą░ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ scratchpad. ą£ą░čüč鹥čĆčā ąĮąĄ ąĮą░ą┤ąŠ ą┐čĆąŠą┤ąŠą╗ąČą░čéčī čćč鹥ąĮąĖąĄ; ąŠąĮ ą╝ąŠąČąĄčé ąĮą░čćą░čéčī ąĮąŠą▓čāčÄ ą┐ąŠą┐čŗčéą║čā ąĘą░ą┐ąĖčüą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ scratchpad. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ čäą╗ą░ą│ AA ą▓ą╝ąĄčüč鹥 čü ąŠčćąĖčēąĄąĮąĮčŗą╝ čäą╗ą░ą│ąŠą╝ PF ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ čĆą░čüą┐ąŠąĘąĮą░ą╗ąŠ ą║ąŠą╝ą░ąĮą┤čā Write.

ąĢčüą╗ąĖ ą▓čüąĄ ą┐čĆąŠčłą╗ąŠ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ, č鹊 ąŠą▒ą░ čŹčéąĖčģ čäą╗ą░ą│ą░ ąŠčćąĖčēąĄąĮčŗ. ąóąĄą┐ąĄčĆčī master ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī čćč鹥ąĮąĖąĄ ąĖ ą┐čĆąŠą▓ąĄčĆą║čā ą║ą░ąČą┤ąŠą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ master ą┐čĆąŠą▓ąĄčĆąĖą╗ ą┤ą░ąĮąĮčŗąĄ, ąŠąĮ ą╝ąŠąČąĄčé ą┐ąŠčüą╗ą░čéčī ą║ąŠą╝ą░ąĮą┤čā Copy Scratchpad. ąŚą░ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ ą┤ąŠą╗ąČąĮčŗ čüą╗ąĄą┤ąŠą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ čéčĆąĄčģ ą░ą┤čĆąĄčüąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓: TA1, TA2 ąĖ E/S. ą£ą░čüč鹥čĆ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą╗čāčćąĖčéčī ą┤ą░ąĮąĮčŗąĄ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ą┐čĆąŠčćąĖčéą░ą▓ scratchpad.

[ąÜąŠą╝ą░ąĮą┤čŗ čäčāąĮą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ]

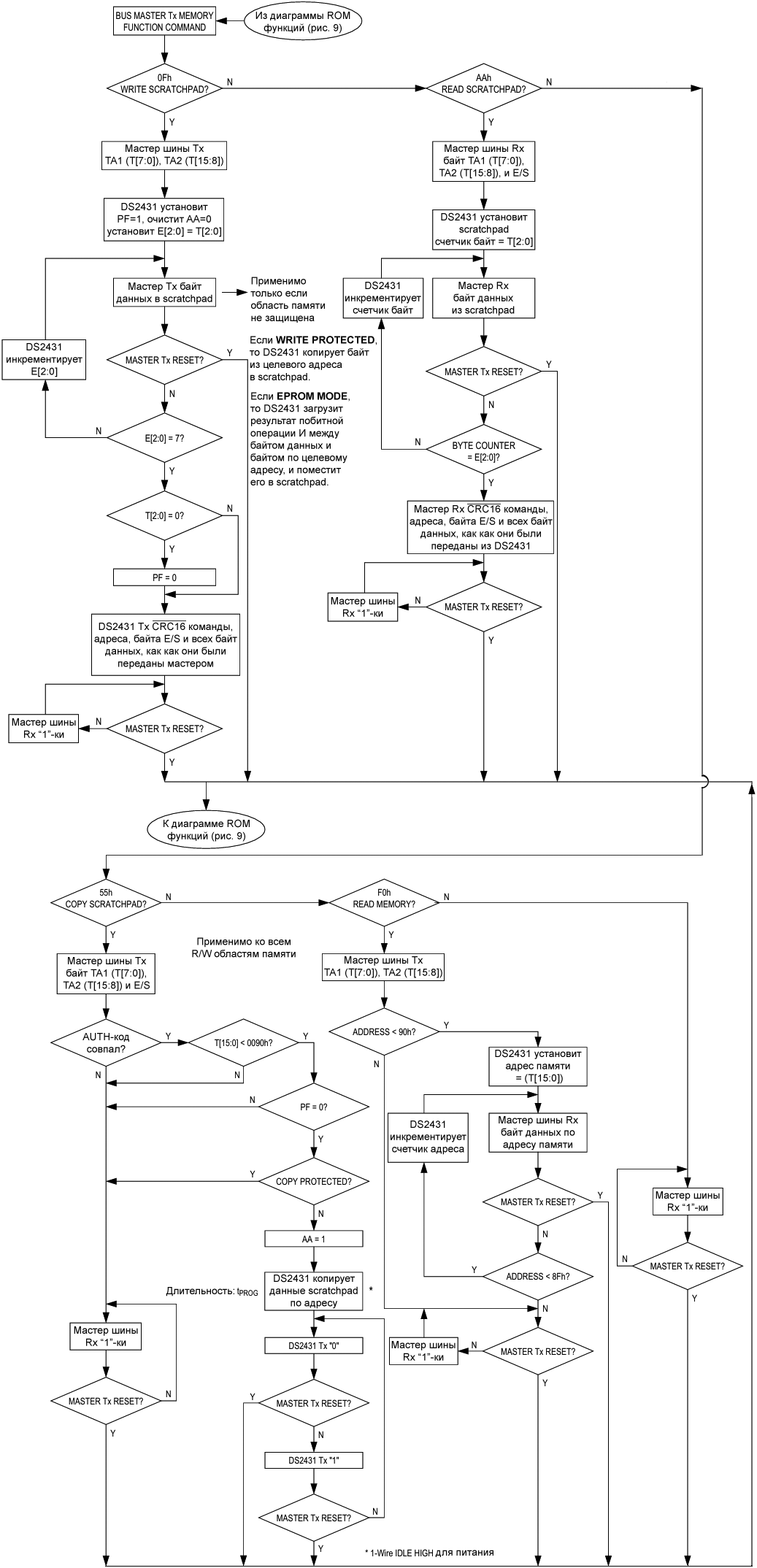

ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ čäčāąĮą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ Memory Function Flowchart (čĆąĖčü. 7) ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą┐čĆąŠč鹊ą║ąŠą╗čŗ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ DS2431. ąÜą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéąĖ čäčāąĮą║čåąĖąĖ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ąĖ čćč鹥ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░, ą╝ąŠąČąĮąŠ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī ą┤ą░ą╗ąĄąĄ ą▓ čüąĄą║čåąĖąĖ "ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čäčāąĮą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ". ąÜąŠą╝ą╝čāąĮąĖą║ą░čåąĖčÅ ą╝ąĄąČą┤čā master ąĖ DS2431 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą╗ąĖą▒ąŠ ąĮą░ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, OD = 0) ąĖą╗ąĖ ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (overdrive speed, OD = 1). ąĢčüą╗ąĖ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čÅą▓ąĮąŠ čĆąĄąČąĖą╝ overdrive, č鹊 DS2431 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ.

Write Scratchpad [0Fh]. ąÜąŠą╝ą░ąĮą┤ą░ Write Scratchpad ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ą░ą┤čĆąĄčüąŠą▓ ą▓ čüčéčĆą░ąĮąĖčåąĄ čĆąĄą│ąĖčüčéčĆą░. ą¦č鹊ą▒čŗ ą┤ą░ąĮąĮčŗąĄ scratchpad ą▒čŗą╗ąĖ ą┤ąŠą┐čāčüčéąĖą╝čŗ ą┤ą╗čÅ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ ą╝ą░čüčüąĖą▓ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą║ąŠą╝ą░ąĮą┤čā Write Scratchpad čü 8 ą▒ą░ą╣čéą░ą╝ąĖ, ąĮą░čćąĖąĮą░čÄčēąĖą╝ąĖčüčÅ ąĮą░ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╝ ą░ą┤čĆąĄčüąĄ ą│čĆą░ąĮąĖčåčŗ čüčéčĆąŠą║ąĖ. ąÜąŠą╝ą░ąĮą┤ą░ Write Scratchpad ą┐čĆąĖą╝ąĄčé ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą░ą┤čĆąĄčüą░ ąĖ čćą░čüčéąĖčćąĮąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüčéčĆąŠą║, ąĮąŠ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ Copy Scratchpad ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ą╗ąŠą║ąĖčĆčāčÄčéčüčÅ.

ą¤ąŠčüą╗ąĄ ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ Write Scratchpad ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī 2 ą▒ą░ą╣čéą░ čåąĄą╗ąĄą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤čāčé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ scratchpad. ąöą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ scratchpad, ąĮą░čćąĖąĮą░čÄčéčüčÅ ąĮą░ čüą╝ąĄčēąĄąĮąĖąĖ ą▒ą░ą╣čéą░ T[2:0]. ąæąĖčéčŗ E[2:0] čĆąĄą│ąĖčüčéčĆą░ E/S ąĘą░ą│čĆčāąČą░čÄčéčüčÅ čüąŠ čüą╝ąĄčēąĄąĮąĖąĄą╝ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą▒ą░ą╣čéą░ ąĖ čāą▓ąĄą╗ąĖčćąĖą▓ą░čÄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ ą▒ą░ą╣č鹊ą╝. ążą░ą║čéąĖč湥čüą║ąĖ E [2:0] - čŹč鹊 čüą╝ąĄčēąĄąĮąĖąĄ ą▒ą░ą╣čéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐ąŠą╗ąĮąŠą│ąŠ ą▒ą░ą╣čéą░, ąĘą░ą┐ąĖčüą░ąĮąĮąŠą│ąŠ ąĮą░ scratchpad. ą¤čĆąĖąĮąĖą╝ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠą╗ąĮčŗąĄ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ.

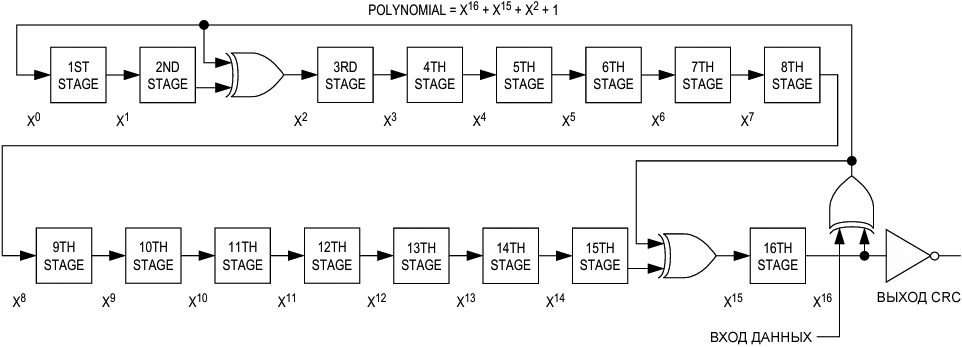

ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ Write Scratchpad, ą│ąĄąĮąĄčĆą░č鹊čĆ CRC ą▓ąĮčāčéčĆąĖ DS2431 (čĆąĖčü. 13) ą▓čŗčćąĖčüą╗čÅąĄčé CRC ąŠčé ą▓čüąĄą│ąŠ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ, ąĮą░čćąĖąĮą░čÅ čü ą║ąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ąĘą░ą║ą░ąĮčćąĖą▓ą░čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą▒ą░ą╣č鹊ą╝ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčüą╗ą░ąĮąĮčŗą╝ master. ąŁčéą░ CRC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąĖąĮąŠą╝ąŠą╝ CRC-16 ą┐čāč鹥ą╝ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ąŠčćąĖčüčéą║ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ CRC ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ čüą┤ą▓ąĖą│ąŠą╝ ą║ąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ Write Scratchpad (0Fh), čåąĄą╗ąĄą▓čŗčģ ą░ą┤čĆąĄčüąŠą▓ (TA1 ąĖ TA2), ąĖ ą▓čüąĄčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ CRC-16 ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčüčÅ čü čäą░ą║čéąĖč湥čüą║ąĖą╝ąĖ TA1, TA2 ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ, ą┐ąŠčüą╗ą░ąĮąĮčŗą╝ąĖ master. ą£ą░čüč鹥čĆ ą╝ąŠąČąĄčé ą┐čĆąĄčĆą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤čā Write Scratchpad ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą▒čŗą╗ ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮąĄčå scratchpad (E[2:0] = 111b), č鹊 master ą╝ąŠąČąĄčé ą┐ąŠčüą╗ą░čéčī 16 čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓ čćč鹥ąĮąĖčÅ ą▒ąĖčé ąĖ ą┐čĆąĖąĮčÅčéčī CRC, čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčāčÄ DS2431.

ąĢčüą╗ąĖ ą║ąŠą╝ą░ąĮą┤ą░ Write Scratchpad ą┐čŗčéą░ąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčīčüčÅ ąĮą░ ąĘą░čēąĖčēąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, č鹊 scratchpad ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ čāąČąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čŹč鹊ą╣ ą┐ą░ą╝čÅčéąĖ ą▓ą╝ąĄčüč鹊 ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ EPROM, č鹊 scratchpad ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┐ąŠą▒ąĖčéąĮčŗą╝ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ ąś (AND) ąŠčé ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ čāąČąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ.

ąĀąĖčü. 7. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ čäčāąĮą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ.

Read Scratchpad [AAh]. ąÜąŠą╝ą░ąĮą┤ą░ Read Scratchpad ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠą▓ąĄčĆąĖčéčī čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ąĖ čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ scratchpad. ą¤ąŠčüą╗ąĄ ą▓čŗą┤ą░čćąĖ ą║ąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ master ąĮą░čćąĖąĮą░ąĄčé čćč鹥ąĮąĖąĄ. ą¤ąĄčĆą▓čŗąĄ 2 ą▒ą░ą╣čéą░ čŹč鹊 čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü. ąĪą╗ąĄą┤čāčÄčēąĖą╝ ą▒ą░ą╣č鹊ą╝ čÅą▓ą╗čÅąĄčéčüčÅ ą║ąŠąĮąĄčćąĮčŗą╣ ą▒ą░ą╣čé čüą╝ąĄčēąĄąĮąĖčÅ/čüąŠčüč鹊čÅąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (ending offset/data status byte, E/S), ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāčÄčé ą┤ą░ąĮąĮčŗąĄ scratchpad, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ąŠčé č鹊ą│ąŠ, čćč鹊 ą╝ą░čüč鹥čĆ ą┐ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮąŠ ąŠčéą┐čĆą░ą▓ąĖą╗. ąŁč鹊 ąŠčüąŠą▒ąĄąĮąĮąŠ ą▓ą░ąČąĮąŠ, ąĄčüą╗ąĖ čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čüčéčĆą░ąĮąĖčåčŗ čĆąĄą│ąĖčüčéčĆą░ ąĖą╗ąĖ čüčéčĆą░ąĮąĖčåčŗ ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ, ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ EPROM. ą£ą░čüč鹥čĆ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠčćąĖčéą░čéčī scratchpad (E[2:0] - T[2:0] + 1 ą▒ą░ą╣čé), ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąŠąĮ ą┐ąŠą╗čāčćą░ąĄčé ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ CRC ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ąŠąĮąĖ ą▒čŗą╗ąĖ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ DS2431. ąĢčüą╗ąĖ ą╝ą░čüč鹥čĆ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čüčćąĖčéčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ CRC, č鹊 ą▓čüąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čÅą▓ą╗čÅčÄčéčüčÅ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ąĖ 1.

Copy Scratchpad [55h]. ąÜąŠą╝ą░ąĮą┤ą░ Copy Scratchpad ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ scratchpad ą▓ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ čüąĄą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ. ą¤ąŠčüą╗ąĄ ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ Copy Scratchpad ą╝ą░čüč鹥čĆ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī 3-ą▒ą░ą╣čéąĮčŗą╣ čłą░ą▒ą╗ąŠąĮ ą░ą▓č鹊čĆąĖąĘą░čåąĖąĖ, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐čĆąĄą┤čłąĄčüčéą▓čāčÄčēąĄą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Read Scratchpad. ąŁč鹊čé 3-ą▒ą░ą╣čéąĮčŗą╣ čłą░ą▒ą╗ąŠąĮ ą┤ąŠą╗ąČąĄąĮ č鹊čćąĮąŠ čüąŠą▓ą┐ą░ą┤ą░čéčī čü ą┤ą░ąĮąĮčŗą╝ąĖ, čüąŠą┤ąĄčƹȹ░čēąĖą╝ąĖčüčÅ ą▓ čéčĆąĄčģ ą░ą┤čĆąĄčüąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░čģ (TA1, TA2, E/S, ą▓ čéą░ą║ąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ). ąĢčüą╗ąĖ čłą░ą▒ą╗ąŠąĮ čüąŠą▓ą┐ą░ą╗, č鹊 čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ą┤ąŠą┐čāčüčéąĖą╝čŗą╣, čäą╗ą░ą│ PF ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ čåąĄą╗ąĄą▓ą░čÅ ą┐ą░ą╝čÅčéčī ąĮąĄ ąĘą░čēąĖčēąĄąĮą░ ąŠčé ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ, č鹊 čäą╗ą░ą│ AA čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ. ąÆčüąĄ 8 ą▒ą░ą╣čé čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ scratchpad ą║ąŠą┐ąĖčĆčāčÄčéčüčÅ ą▓ čåąĄą╗ąĄą▓čāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ. ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čŹč鹊ą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čüąŠčüčéą░ą▓ą╗čÅąĄčé tPROG (ą╝ą░ą║čüąĖą╝čāą╝ ąŠčé 10 ą╝čü ą┤ąŠ 12.5 ą╝čü, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓ąĄčĆčüąĖąĖ A1 ąĖą╗ąĖ A2, čüą╝. ą┤ą░čéą░čłąĖčé [1]), ą▓ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ čłąĖąĮąĄ 1-Wire ąĮąĄ ą┤ąŠą╗ąČąĮąŠ čāą┐ą░čüčéčī ąĮąĖąČąĄ 2.8V. ą©ą░ą▒ą╗ąŠąĮ č湥čĆąĄą┤čāčÄčēąĖčģčüčÅ ąĮčāą╗ąĄą╣ ąĖ ąĮčāą╗ąĄą╣ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ master ąĮąĄ ą▓čŗą┤ą░čüčé ąĖą╝ą┐čāą╗čīčü čüą▒čĆąŠčüą░. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ PF ąĖą╗ąĖ čåąĄą╗ąĄą▓ą░čÅ ą┐ą░ą╝čÅčéčī ąĘą░čēąĖčēąĄąĮą░ ąŠčé ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ, č鹊 ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ąĖ čäą╗ą░ą│ AA ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ.

Read Memory [F0h]. ąÜąŠą╝ą░ąĮą┤ą░ Read Memory čŹč鹊 ąŠčüąĮąŠą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ DS2431. ą¤ąŠčüą╗ąĄ ą▓čŗą┤ą░čćąĖ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ master ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī 2 ą▒ą░ą╣čéą░ čåąĄą╗ąĄą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░. ą¤ąŠčüą╗ąĄ čŹčéąĖčģ 2 ą▒ą░ą╣čé master čćąĖčéą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ąĮą░čćąĖąĮą░čÅ čü čåąĄą╗ąĄą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░, ąĖ ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī čćč鹥ąĮąĖčÅ, ą┐ąŠą║ą░ ą░ą┤čĆąĄčü ąĮąĄ ą┐čĆąĄą▓čŗčłą░ąĄčé 008Fh. ąĢčüą╗ąĖ master ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čćč鹥ąĮąĖąĄ, č鹊 čĆąĄąĘčāą╗čīčéą░č鹊ą╝ ą▒čāą┤čāčé ą╗ąŠą│ąĖč湥čüą║ąĖąĄ ąĄą┤ąĖąĮąĖčåčŗ. ąÜąŠą╝ą░ąĮą┤ą░ Read Memory ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ TA1, TA2, E/S ąĖ ąĮą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ scratchpad.

[1-Wire Bus System]

ą©ąĖąĮą░ 1-Wire čŹčéą░ čüąĖčüč鹥ą╝ą░, ą▓ ą║ąŠč鹊čĆąŠą╣ čüčāčēąĄčüčéą▓čāąĄčé ąŠą┤ąĖąĮ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ (master) ąĖ ąŠą┤ąĮąŠ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (slave). ąÆčüąĄ 菹║ąĘąĄą╝ą┐ą╗čÅčĆčŗ DS2431 čŹč鹊 slave-čāčüčéčĆąŠą╣čüčéą▓ą░. Master čłąĖąĮčŗ čŹč鹊 ąŠą▒čŗčćąĮąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ą×ą▒čüčāąČą┤ąĄąĮąĖąĄ čüąĖčüč鹥ą╝čŗ čłąĖąĮčŗ čĆą░ąĘą▒ąĖč鹊 ąĮą░ 3 č鹥ą╝čŗ: "ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ", "ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čéčĆą░ąĮąĘą░ą║čåąĖąĖ" ąĖ "ąĪąĖą│ąĮą░ą╗čŗ 1-Wire" (čéąĖą┐čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ ąĖčģ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ, ąĖą╗ąĖ čéą░ą╣ą╝ąĖąĮą│). ą¤čĆąŠč鹊ą║ąŠą╗ 1-Wire ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čéčĆą░ąĮąĘą░ą║čåąĖąĖ čłąĖąĮčŗ ą▓ č鹥čĆą╝ąĖąĮą░čģ čüąŠčüč鹊čÅąĮąĖčÅ čłąĖąĮčŗ ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠąĮą║čĆąĄčéąĮčŗčģ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓, ą║ąŠč鹊čĆčŗąĄ ąĖąĮąĖčåąĖąĖčĆčāčÄčéčüčÅ ąĮą░ ą┐ą░ą┤ą░čÄčēąĄą╝ čäčĆąŠąĮč鹥 čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüąŠą▓ (ąĖčģ č乊čĆą╝ąĖčĆčāąĄčé master).

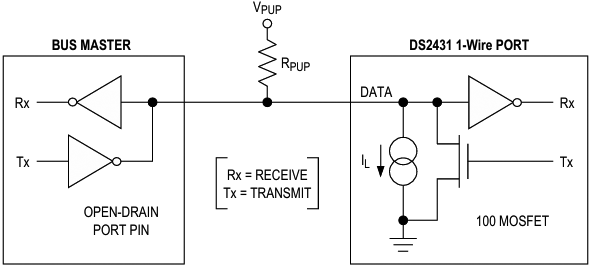

ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. ą©ąĖąĮą░ 1-Wire ą┐ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÄ ąĖą╝ąĄąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĮčā čüąĖą│ąĮą░ą╗čīąĮčāčÄ ą╗ąĖąĮąĖčÄ. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ą║ą░ąČą┤ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī čüąĖą│ąĮą░ą╗ąŠą╝ č鹊ą╗čīą║ąŠ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ. ą¦č鹊ą▒čŗ čŹč鹊 čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī, ą║ą░ąČą┤ąŠąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠąĄ ą║ čłąĖąĮąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ čüąŠą┤ąĄčƹȹ░čéčī ą▓ čüąĄą▒ąĄ ą▓čŗčģąŠą┤ąĮąŠą╣ ą║ą╗čÄčć čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 č湥ą│ąŠ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ąŠąĘą╝ąŠąČąĮčŗą╝ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĮą░ ą▓čŗčģąŠą┤ąĄ čéčĆąĖ čüąŠčüč鹊čÅąĮąĖčÅ čłąĖąĮčŗ (ą╗ąŠą│. 0, ą╗ąŠą│. 1, ąŠčéą║ą╗čÄč湥ąĮąŠ). ąÜą░ą║ čĆą░ąĘ čéą░ą║ąŠą╣ 1-Wire ą┐ąŠčĆčé ą▓ ą▓ąĖą┤ąĄ ąŠčéą║čĆčŗč鹊ą│ąŠ čüč鹊ą║ą░ ąĖ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ čā DS2431, ąĄą│ąŠ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ čüčģąĄą╝ą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 8.

ą£ąĮąŠą│ąŠč鹊č湥čćąĮą░čÅ čłąĖąĮą░ 1-Wire čüąŠąĄą┤ąĖąĮčÅąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ ąĖ ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ. DS2431 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 2 čĆąĄąČąĖą╝ą░ čüą║ąŠčĆąŠčüčéąĖ ąŠą▒ą╝ąĄąĮą░: standard (15.4kbps max) ąĖ overdrive (125kbps max). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 legacy-ąĖąĘą┤ąĄą╗ąĖčÅ 1-Wire ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čüą║ąŠčĆąŠčüčéčī standard 16.3kbps ąĖ overdrive 142kbps. ąØąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĄąĮčīčłą░čÅ čüą║ąŠčĆąŠčüčéčī ą┤ą╗čÅ DS2431 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąĖąĘ-ąĘą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą▓ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī ą▒čŗą╗ąĖ ąŠą▒čāčüą╗ąŠą▓ą╗ąĄąĮčŗ ą┐ąŠą▓čŗčłąĄąĮąĖąĄą╝ ąĮą░ą┤ąĄąČąĮąŠčüčéąĖ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ 1-Wire ą▓ ą┐ą╗ą░ąĮąĄ čāčüč鹊ą╣čćąĖą▓ąŠčüčéąĖ ą║ ą┐ąŠą╝ąĄčģą░ą╝. ąŚąĮą░č湥ąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą│ąŠ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ čłąĖąĮčŗ (pullup) ąĘą░ą▓ąĖčüąĖčé ą│ą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠčé čĆą░ąĘą╝ąĄčĆą░ čüąĄčéąĖ ąĖ čāčüą╗ąŠą▓ąĖą╣ ąĮą░ą│čĆčāąĘą║ąĖ. DS2431 čéčĆąĄą▒čāąĄčé pullup 2.2k╬® (max) ąĮą░ ą╗čÄą▒ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ.

ąĪąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle) čłąĖąĮčŗ 1-Wire čŹč鹊 ą╗ąŠą│. 1. ąĢčüą╗ąĖ ą┐ąŠ ą║ą░ą║ąŠą╣-č鹊 ą┐čĆąĖčćąĖąĮąĄ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮą░, čłąĖąĮą░ ą┤ąŠą╗ąČąĮą░ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮą░. ąØąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ čłąĖąĮą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0 ą┤ąŠą╗čīčłąĄ č湥ą╝ 16 ą╝ą║čü (čĆąĄąČąĖą╝ čüą║ąŠčĆąŠčüčéąĖ overdrive) ąĖą╗ąĖ ą┤ąŠą╗čīčłąĄ č湥ą╝ 120 ą╝ą║čü (čĆąĄąČąĖą╝ čüą║ąŠčĆąŠčüčéąĖ standard), ąĖąĮą░č湥 ąŠą┤ąĮąŠ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠą│čāčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮčŗ.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ą¤čĆąŠč鹊ą║ąŠą╗ ą┤ąŠčüčéčāą┐ą░ ą║ DS2431 ą┐ąŠ čłąĖąĮąĄ 1-Wire čüą╗ąĄą┤čāčÄčēąĖą╣:

ŌŚÅ ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ

ŌŚÅ ąÜąŠą╝ą░ąĮą┤ą░ čäčāąĮą║čåąĖąĖ ROM

ŌŚÅ ąÜąŠą╝ą░ąĮą┤ą░ čäčāąĮą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ

ŌŚÅ ąóčĆą░ąĮąĘą░ą║čåąĖčÅ/ą┤ą░ąĮąĮčŗąĄ

ąĀąĖčü. 8. ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ.

ąÆčüąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąĮą░ čłąĖąĮąĄ 1-Wire ąĮą░čćąĖąĮą░čÄčéčüčÅ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čüąŠčüč鹊ąĖčé ąĖąĘ ąĖą╝ą┐čāą╗čīčüą░ reset (ą╗ąŠą│. 0 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ tRSTL, 480 .. 640 ą╝ą║čü ąĮą░ čüą║ąŠčĆąŠčüčéąĖ standard ąĖą╗ąĖ 48 .. 80 ą╝ą║čü ąĮą░ čüą║ąŠčĆąŠčüčéąĖ overdrive), č乊čĆą╝ąĖčĆčāąĄą╝čŗą╣ ą╝ą░čüč鹥čĆąŠą╝, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé ąĖą╝ą┐čāą╗čīčü (ąĖą╝ą┐čāą╗čīčüčŗ) ą┐čĆąĖčüčāčéčüčéą▓ąĖčÅ (presence pulse), č乊čĆą╝ąĖčĆčāąĄą╝čŗą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ). Presence pulse ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ą░čüč鹥čĆčā čłąĖąĮčŗ čāąĘąĮą░čéčī, čćč鹊 ąĮą░ čłąĖąĮąĄ ąĄčüčéčī DS2431, ąĖ ąŠąĮą░ ą│ąŠč鹊ą▓ą░ ą║ čĆą░ą▒ąŠč鹥. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąĪąĖą│ąĮą░ą╗čŗ 1-Wire".

[ąÜąŠą╝ą░ąĮą┤čŗ čäčāąĮą║čåąĖą╣ ROM]

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ąĮą░ą╗ąĖčćąĖąĄ ąĖą╝ą┐čāą╗čīčüą░ presence, ąŠąĮ ą╝ąŠąČąĄčé ą▓čŗą┤ą░čéčī ąĮą░ čłąĖąĮčā 7 ą║ąŠą╝ą░ąĮą┤ čäčāąĮą║čåąĖąĖ ROM, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé DS2431. ąÆčüąĄ čŹčéąĖ ą║ąŠą╝ą░ąĮą┤čŗ ROM ąĖą╝ąĄčÄčé ą┤ą╗ąĖąĮčā 8 ą▒ąĖčé. ąĪą┐ąĖčüąŠą║ čŹčéąĖčģ ą║ąŠą╝ą░ąĮą┤ čüą╗ąĄą┤čāčÄčēąĖą╣ (čüą╝. ą░ą╗ą│ąŠčĆąĖčéą╝ ąĮą░ čĆąĖčü. 9).

Read ROM [33h]. ąÜąŠą╝ą░ąĮą┤ą░ Read ROM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ą░čüč鹥čĆčā čłąĖąĮčŗ ą┐čĆąŠčćąĖčéą░čéčī ąĖąĘ DS2431 ąĄčæ 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ family code, čāąĮąĖą║ą░ą╗čīąĮčŗą╣ 48-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüąĄčĆąĖą╣ąĮčŗą╣ ąĮąŠą╝ąĄčĆ ąĖ 8-čĆą░ąĘčĆčÅą┤ąĮčāčÄ CRC. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąĮą░ čłąĖąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąĢčüą╗ąĖ ąĮą░ čłąĖąĮąĄ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓, č鹊 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą║ąŠą╗ą╗ąĖąĘąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą▓čüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĮą░čćąĮčāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ (ąĖčģ ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║ čüč乊čĆą╝ąĖčĆčāąĄčé ąĮą░ čłąĖąĮąĄ čĆąĄąĘčāą╗čīčéą░čé ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ "ą╝ąŠąĮčéą░ąČąĮąŠąĄ ąś"). ąÆ čéą░ą║ąŠą╣ čüąĖčéčāą░čåąĖąĖ family code ąĖ 48-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüąĄčĆąĖą╣ąĮčŗą╣ ąĮąŠą╝ąĄčĆ ą┤ą░ą┤čāčé ąĮąĄą▓ąĄčĆąĮčŗą╣ ą║ąŠą┤ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ CRC.

Match ROM [55h]. ąÜąŠą╝ą░ąĮą┤ą░ Match ROM, ąĘą░ ą║ąŠč鹊čĆčŗą╣ ąĖą┤ąĄčé 64-čĆą░ąĘčĆčÅą┤ąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ROM, ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ą░čüč鹥čĆčā čłąĖąĮčŗ ą░ą┤čĆąĄčüąŠą▓ą░čéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ DS2431, ą║ąŠą│ą┤ą░ ąĮą░ čłąĖąĮąĄ ąĖčģ ąĮąĄčüą║ąŠą╗čīą║ąŠ. ąØą░ ą┐ąŠčüą╗ąĄą┤čāčÄčēčāčÄ ą║ąŠą╝ą░ąĮą┤čā čäčāąĮą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ ąŠčéą▓ąĄčéąĖčé č鹊ą╗čīą║ąŠ č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ DS2431, čā ą║ąŠč鹊čĆąŠą│ąŠ č鹊čćąĮąŠ čüąŠą▓ą┐ą░ą╗ą░ 64-čĆą░ąĘčĆčÅą┤ąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ROM. ąÆčüąĄ ą┤čĆčāą│ąĖąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒čāą┤čāčé ąČą┤ą░čéčī ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüą░ reset, ąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ čü ąŠą┤ąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ąĮą░ čłąĖąĮąĄ, čéą░ą║ ąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ.

Search ROM [F0h]. ąÜąŠą│ą┤ą░ čüąĖčüč鹥ą╝ą░ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą╝ąŠąČąĄčé ąĮąĄ ąĘąĮą░čéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ ąĖą╗ąĖ ąĖčģ čĆąĄą│ąĖčüčéčĆą░čåąĖąŠąĮąĮčŗąĄ ąĮąŠą╝ąĄčĆą░ (64-ą▒ąĖčéąĮčŗąĄ ROM-ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, čāąĮąĖą║ą░ą╗čīąĮčŗąĄ ą┤ą╗čÅ ą╗čÄą▒ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ 1-Wire). ąæą╗ą░ą│ąŠą┤ą░čĆčÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čłąĖąĮčŗ ą▓ ą▓ąĖą┤ąĄ "ą╝ąŠąĮčéą░ąČąĮąŠą│ąŠ ąś" ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąŠčåąĄčüčü ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą┤ą╗čÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ čĆąĄą│ąĖčüčéčĆą░čåąĖąŠąĮąĮčŗčģ ąĮąŠą╝ąĄčĆąŠą▓ ą▓čüąĄčģ slave-čāčüčéčĆąŠą╣čüčéą▓. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▒ąĖčéą░ 64-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░čåąĖąŠąĮąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░ ROM, ąĮą░čćąĖąĮą░čÅ čü čüą░ą╝ąŠą│ąŠ ą╝ą╗ą░ą┤čłąĄą│ąŠ ąĘąĮą░čćą░čēąĄą│ąŠ ą▒ąĖčéą░, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą▓čŗą┤ą░ąĄčé čéčĆąĖą┐ą╗ąĄčé ą▓čĆąĄą╝ąĄąĮąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓. ąÆ ą┐ąĄčĆą▓ąŠą╝ čüą╗ąŠč鹥 ą║ą░ąČą┤ąŠąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čāčćą░čüčéą▓čāčÄčēąĄąĄ ą▓ ą┐ąŠąĖčüą║ąĄ, ą▓čŗą▓ąŠą┤ąĖčé ąĖčüčéąĖąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüą▓ąŠąĄą│ąŠ ą▒ąĖčéą░ čĆąĄą│ąĖčüčéčĆą░čåąĖąŠąĮąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░. ąÆąŠ ą▓č鹊čĆąŠą╝ čüą╗ąŠč鹥 ą║ą░ąČą┤ąŠąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čāčćą░čüčéą▓čāčÄčēąĄąĄ ą▓ ą┐ąŠąĖčüą║ąĄ, ą▓čŗą▓ąŠą┤ąĖčé ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĮąŠąĄ (ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮąŠąĄ) ąĘąĮą░č湥ąĮąĖąĄ čüą▓ąŠąĄą│ąŠ ą▒ąĖčéą░ čĆąĄą│ąĖčüčéčĆą░čåąĖąŠąĮąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░. ąÆ čéčĆąĄčéčīąĄą╝ čüą╗ąŠč鹥 master ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▓ąĄčĆąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒ąĖčéą░. ąÆčüąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░, čā ą║ąŠč鹊čĆčŗčģ ąĮąĄ čüąŠą▓ą┐ą░ą╗ ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ čéčĆąĄčéąĖą╣ ą▒ąĖčé, ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé čüą▓ąŠąĄ čāčćą░čüčéąĖąĄ ą▓ ą┐ąŠąĖčüą║ąĄ (ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ąĖą╝ą┐čāą╗čīčüą░ reset). ąĢčüą╗ąĖ ąŠą▒ą░ čüčćąĖčéą░ąĮąĮčŗąĄ ą▒ąĖčéą░ 0, č鹊 ą╝ą░čüč鹥čĆ ąĘąĮą░ąĄčé, čćč鹊 ąĮą░ čłąĖąĮąĄ ąĄčüčéčī ą┤ą▓ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ čü ąŠą▒ąŠąĖą╝ąĖ čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ čŹč鹊ą│ąŠ ą▒ąĖčéą░. ą¤čĆąĖ ą▓čŗą▒ąŠčĆąĄ, ą║ą░ą║ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą┐ąĖčüą░čéčī, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé ą▓ąĄčéą▓ą╗ąĄąĮąĖčÅ ą┐ąŠ ą┤ąĄčĆąĄą▓čā ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą║ąŠą┤ąŠą▓ ROM. ą¤ąŠčüą╗ąĄ ąŠą┤ąĮąŠą│ąŠ ą┐ąŠą╗ąĮąŠą│ąŠ ą┐čĆąŠčģąŠą┤ą░ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąĘąĮą░ąĄčé čĆąĄą│ąĖčüčéčĆą░čåąĖąŠąĮąĮčŗą╣ ąĮąŠą╝ąĄčĆ ąŠą┤ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą┐čĆąŠčģąŠą┤čŗ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čĆąĄą│ąĖčüčéčĆą░čåąĖąŠąĮąĮčŗąĄ ąĮąŠą╝ąĄčĆą░ ąŠčüčéą░ą╗čīąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąĪą╝. ą░ą┐ąĮąŠčāčé [3], ą│ą┤ąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüą░ąĮ ą░ą╗ą│ąŠčĆąĖčéą╝ ą┐ąŠąĖčüą║ą░ čāčüčéčĆąŠą╣čüčéą▓, ą▓ą║ą╗čÄčćą░čÅ ą┐čĆąĖą╝ąĄčĆ.

Skip ROM [CCh]. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé 菹║ąŠąĮąŠą╝ąĖčéčī ą▓čĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░, ą║ąŠą│ą┤ą░ ą║ čłąĖąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ čŹč鹊ą╝čā ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čäčāąĮą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ ą╝ą░čüč鹥čĆčā ąĮąĄ ąĮčāąČąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčéčī 64-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ROM-ą║ąŠą┤. ąĢčüą╗ąĖ ąČąĄ ąĮą░ čłąĖąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠčćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, č鹊 ą┐čĆąĖ ą▓čŗą┤ą░č湥 ą║ąŠą╝ą░ąĮą┤čŗ Skip ROM ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą║ąŠą╗ą╗ąĖąĘąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░čćąĮčāčé ą┐ąĄčĆąĄą┤ą░čćčā ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

ąĀąĖčü. 9. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ čäčāąĮą║čåąĖą╣ ROM.

Resume [A5h]. ąöą╗čÅ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą┐čĆąŠą┐čāčüą║ąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą▓ čüąĖčéčāą░čåąĖąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ čüčāčēąĄčüčéą▓čāąĄčé ą║ąŠą╝ą░ąĮą┤ą░ Resume. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┐čĆąŠą▓ąĄčĆčÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ RC, ąĖ ąĄčüą╗ąĖ ąŠąĮ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą┐ąĄčĆąĄą┤ą░ąĄčé ąĮą░ą┐čĆčÅą╝čāčÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤ą░ą╝ čäčāąĮą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠą┤ąŠą▒ąĮąŠ ą║ąŠą╝ą░ąĮą┤ąĄ Skip ROM. ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╣ čüą┐ąŠčüąŠą▒ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé RC - čāčüą┐ąĄčłąĮąŠąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤ Match ROM, Search ROM ąĖą╗ąĖ Overdrive-Match ROM. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒ąĖčé RC čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ čāčüčéčĆąŠą╣čüčéą▓čā ą╝ąŠąČąĮąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ č湥čĆąĄąĘ ą║ąŠą╝ą░ąĮą┤čā Resume. ąöąŠčüčéčāą┐ ą║ ą┤čĆčāą│ąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ąĮą░ čłąĖąĮąĄ ąŠčćąĖčüčéąĖčé ą▒ąĖčé RC, č湥ą╝ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčéčüčÅ ąŠčéą▓ąĄčé ąĮą░ ą║ąŠą╝ą░ąĮą┤čā Resume čüąŠ čüč鹊čĆąŠąĮčŗ ą┤ą▓čāčģ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ slave-čāčüčéčĆąŠą╣čüčéą▓.

Overdrive-Skip ROM [3Ch]. ąÆ čüąĖčéčāą░čåąĖčÅčģ čü ąŠą┤ąĮąĖą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ąĮą░ čłąĖąĮąĄ čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┐ąŠąĘą▓ąŠą╗ąĖčé 菹║ąŠąĮąŠą╝ąĖčéčī ą▓čĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ą╝ą░čüč鹥čĆčā ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čäčāąĮą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ ą▒ąĄąĘ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ 64-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ ROM-ą║ąŠą┤ą░. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąŠą▒čŗčćąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ Skip ROM, ą║ąŠą╝ą░ąĮą┤ą░ Overdrive-Skip ROM čāčüčéą░ąĮąŠą▓ąĖčé DS2431 ą▓ čĆąĄąČąĖą╝ overdrive (ą┐ąŠą▓čŗčłąĄąĮąĮą░čÅ čüą║ąŠčĆąŠčüčéčī, OD = 1). ą¤ąŠčüą╗ąĄ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą▓ąĄčüčī ąŠą▒ą╝ąĄąĮ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ąĮą░ čüą║ąŠčĆąŠčüčéąĖ overdrive, ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠčüčéčāą┐ąĖčé ąĖą╝ą┐čāą╗čīčü reset ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ąĮąĄ ą╝ąĄąĮčīčłąĄ 480 ą╝ą║čü, čćč鹊 čüą▒čĆąŠčüąĖčé slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ ą▓ čĆąĄąČąĖą╝ čüą║ąŠčĆąŠčüčéąĖ standard (OD = 0).

ąÜąŠą│ą┤ą░ čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą▓čŗą┤ą░ąĮą░ ąĮą░ čłąĖąĮąĄ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą▓čüąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖąĄ čĆąĄąČąĖą╝ overdrive ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčüčÅ ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮčāčÄ čüą║ąŠčĆąŠčüčéčī. ąöą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĄą│ąŠ overdrive čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą┤ą░ąĮ ąĖą╝ą┐čāą╗čīčü reset ąĮą░ čüą║ąŠčĆąŠčüčéąĖ overdrive (ą╗ąŠą│. 0 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 48 .. 80 ą╝ą║čü), ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┤ąŠą╗ąČąĮą░ ąĖą┤čéąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą╝ą░ąĮą┤čŗ Match ROM ąĖą╗ąĖ Search ROM. ąŁč鹊 čüąŠą║čĆą░čēą░ąĄčé ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄčüčüą░ ą┐ąŠąĖčüą║ą░. ąĢčüą╗ąĖ ąĮą░ čłąĖąĮąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖčģ overdrive čāčüčéčĆąŠą╣čüčéą▓, ąĖ ą┐ąŠčüą╗ąĄ ą║ąŠą╝ą░ąĮą┤čŗ Overdrive-Skip ROM ą┐ąŠčüą╗ąĄą┤čāąĄčé ą║ąŠą╝ą░ąĮą┤ą░ čćč鹥ąĮąĖčÅ, č鹊 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą║ąŠą╗ą╗ąĖąĘąĖčÅ ąĮą░ čłąĖąĮąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

Overdrive-Match ROM [69h]. ąÜąŠą╝ą░ąĮą┤ą░ Overdrive-Match ROM, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤ąĄčé 64-ą▒ąĖčéąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ROM-ą║ąŠą┤ą░, ą┐ąĄčĆąĄą┤ą░ąĮąĮą░čÅ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ overdrive, ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ą░čüč鹥čĆčā čłąĖąĮčŗ ą░ą┤čĆąĄčüąŠą▓ą░čéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ DS2431, ą║ąŠą│ą┤ą░ ą║ čłąĖąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓, ąĖ ąŠąĮąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ overdrive. ąØą░ ą┐ąŠčüą╗ąĄą┤čāčÄčēčāčÄ ą║ąŠą╝ą░ąĮą┤čā čäčāąĮą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ ąŠčéą▓ąĄčéąĖčé č鹊ą╗čīą║ąŠ č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ DS2431, čā ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą┐ą░ą╗ 64-ą▒ąĖčéąĮčŗą╣ ROM-ą║ąŠą┤. Slave-čāčüčéčĆąŠą╣čüčéą▓ą░, čāąČąĄ ąĮą░čģąŠą┤čÅčēąĖąĄčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ overdrive ąŠčé ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ą║ąŠą╝ą░ąĮą┤čŗ Overdrive-Skip ROM ąĖą╗ąĖ čāčüą┐ąĄčłąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ Overdrive-Match ROM, ąŠčüčéą░čÄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ overdrive. ąÆčüąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖąĄ čĆąĄąČąĖą╝ overdrive čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ąŠąĘą▓čĆą░čéčÅčéčüčÅ ą║ čüą║ąŠčĆąŠčüčéąĖ standard speed ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ąĖą╝ą┐čāą╗čīčüąĄ reset čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 480 ą╝ą║čü. ąÜąŠą╝ą░ąĮą┤ą░ Overdrive-Match ROM ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĖ čü ąŠą┤ąĮąĖą╝, ąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ.

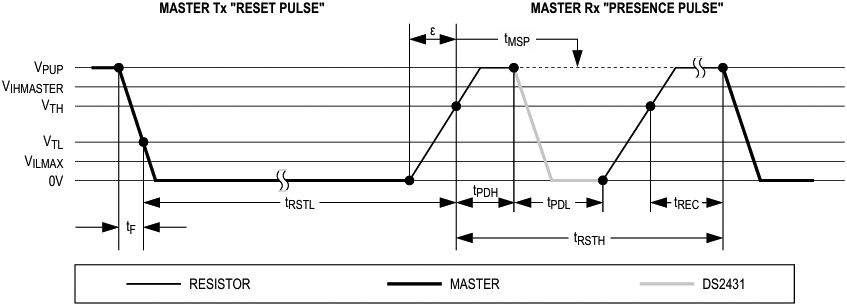

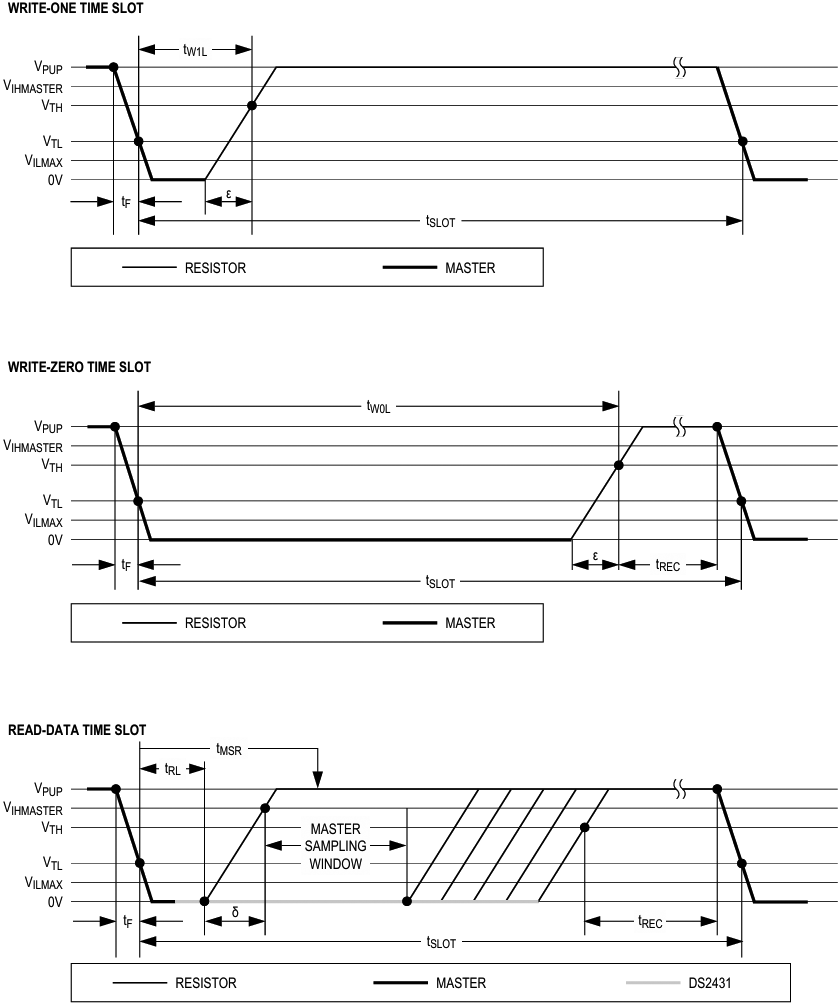

ąĪąĖą│ąĮą░ą╗čŗ 1-Wire. DS2431 čéčĆąĄą▒čāąĄčé ąČąĄčüčéą║ąĖčģ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ ą┤ą╗čÅ ą│ą░čĆą░ąĮčéąĖąĖ čåąĄą╗ąŠčüčéąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ. ąŁčéąĖ ą┐čĆąŠč鹊ą║ąŠą╗čŗ čüąŠčüč鹊čÅčé ąĖąĘ 4 čéąĖą┐ąŠą▓ čüąĖą│ąĮą░ą╗ąŠą▓, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą┐čĆąŠą▓ąŠą┤čā čłąĖąĮčŗ: ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüą▒čĆąŠčüą░ čü ąĖą╝ą┐čāą╗čīčüąŠą╝ reset ąĖ ąĖą╝ą┐čāą╗čīčüąŠą╝ presence, ąĘą░ą┐ąĖčüčī 0 (write-zero), ąĘą░ą┐ąĖčüčī 1 (write-one) ąĖ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ (read-data). ąŚą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ąĖą╝ą┐čāą╗čīčüą░ presence, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą▓čüąĄ čüą┐ą░ą┤čŗ čāčĆąŠą▓ąĮčÅ ąŠčé 1 ą║ 0. DS2431 ą╝ąŠąČąĄčé ąŠą▒ą╝ąĄąĮąĖą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ ąĮą░ ą┤ą▓čāčģ čĆą░ąĘąĮčŗčģ čüą║ąŠčĆąŠčüčéčÅčģ: standard ąĖ overdrive. ąĢčüą╗ąĖ čÅą▓ąĮąŠ ąĮąĄ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆąĄąČąĖą╝ overdrive, č鹊 DS2431 čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čüą║ąŠčĆąŠčüčéąĖ standard. ąÆ čĆąĄąČąĖą╝ąĄ overdrive ą▒čŗčüčéčĆčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ą┤ąĄą╣čüčéą▓čāčÄčé ą┤ą╗čÅ ą▓čüąĄčģ č乊čĆą╝ čüąĖą│ąĮą░ą╗ąŠą▓.

ą¦č鹊ą▒čŗ ą┐ąĄčĆąĄą╣čéąĖ ąĖąĘ čĆąĄąČąĖą╝ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ ą▓ ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄąČąĖą╝, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą╗ąĖąĮąĖąĖ 1-Wire ą┤ąŠą╗ąČąĮąŠ čāą┐ą░čüčéčī čü VPUP ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ VTL. ą¦č鹊ą▒čŗ ą┐ąĄčĆąĄą╣čéąĖ ąĖąĘ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐ąŠą┤ąĮąĖą╝ą░čéčīčüčÅ ąŠčé VILMAX ą▓čŗčłąĄ ą┐ąŠčĆąŠą│ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ VTH. ąÆčĆąĄą╝čÅ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠąĄ ą┤ą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 10 ą║ą░ą║ ╬Ą, ąĖ ąĄą│ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖč鹥ą╗čīąĮąŠčüčéčī ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ą┐ąŠą┤čéčÅąČą║ąĖ (RPUP) ąĖ ąĄą╝ą║ąŠčüčéąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ 1-Wire čüąĄčéąĖ. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ VILMAX ą░ą║čéčāą░ą╗čīąĮąŠ ą┤ą╗čÅ DS2431 ą┐čĆąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĖ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, ąĮąĄ ą▓čŗąĘčŗą▓ą░čÅ ąĮąĖą║ą░ą║ąĖčģ čüąŠą▒čŗčéąĖą╣.

ąĀąĖčü. 10 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, čéčĆąĄą▒čāąĄą╝čāčÄ ą┤ą╗čÅ ąĮą░čćą░ą╗ą░ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ čü DS2431. ąĢčüą╗ąĖ ąĘą░ ąĖą╝ą┐čāą╗čīčüąŠą╝ reset čüą╗ąĄą┤čāąĄčé ąĖą╝ą┐čāą╗čīčü presence, č鹊 čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ą╗čÅ ą╝ą░čüč鹥čĆą░, čćč鹊 DS2431 ą│ąŠč鹊ą▓ąŠ ą║ ą┐čĆąĖąĄą╝čā ą┤ą░ąĮąĮčŗčģ ą║ąŠčĆčĆąĄą║čéąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ ROM ąĖ ą║ąŠą╝ą░ąĮą┤ čäčāąĮą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ. ąĢčüą╗ąĖ ą╝ą░čüč鹥čĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą║ąŠčĆąŠčüčéčīčÄ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ (slew-rate control on falling edge), č鹊 ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą┤čéčÅąĮčāčéčī čüąĖą│ąĮą░ą╗ ą║ ą╗ąŠą│. 0 ąĮą░ ą▓čĆąĄą╝čÅ tRSTL + tF ą┤ą╗čÅ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĖ ą▓čĆąĄą╝ąĄąĮąĖ čüą┐ą░ą┤ą░. ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĖą╝ą┐čāą╗čīčüą░ čüą▒čĆąŠčüą░ tRSTL 480 ą╝ą║čü ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą▓čŗčģąŠą┤čā slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ overdrive (ąĄčüą╗ąĖ ąŠąĮ ą┤ąĄą╣čüčéą▓ąŠą▓ą░ą╗), čćč鹊 ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠ ą▓ąŠąĘą▓čĆą░čēą░ąĄčé slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čüą║ąŠčĆąŠčüčéčī standard. ąĢčüą╗ąĖ DS2431 ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ overdrive, ąĖ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī tRSTL ąĮąĄ ą▒ąŠą╗čīčłąĄ 80 ą╝ą║čü, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ overdrive. ąĢčüą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čĆąĄąČąĖą╝ąĄ overdrive, ąĖ tRSTL ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą╝ąĄąČą┤čā 80 ą╝ą║čü ąĖ 480 ą╝ą║čü, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą▒čĆąŠčüąĖčéčüčÅ, ąĮąŠ čüą║ąŠčĆąŠčüčéčī ąŠą▒ą╝ąĄąĮą░ čüčéą░ąĮąĄčé ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ master ąŠčüą▓ąŠą▒ąŠą┤ąĖą╗ čłąĖąĮčā, ąŠąĮ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ą┐čĆąĖąĄą╝ą░. ąóąĄą┐ąĄčĆčī čłąĖąĮą░ 1-Wire ą┐ąŠą┤čéčÅąĮčāčéą░ ą║ čāčĆąŠą▓ąĮčÄ VPUP č湥čĆąĄąĘ pullup čĆąĄąĘąĖčüč鹊čĆ, ąĖą╗ąĖ ą▓ čüą╗čāčćą░ąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ DS2482-x00 ąĖą╗ąĖ DS2480B č湥čĆąĄąĘ ą░ą║čéąĖą▓ąĮčāčÄ čüčģąĄą╝čā. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐ąĄčĆąĄčģąŠą┤ č湥čĆąĄąĘ ą┐ąŠčĆąŠą│ VTH, DS2431 ąČą┤ąĄčé ą▓ č鹥č湥ąĮąĖąĄ ą▓čĆąĄą╝ąĄąĮąĖ tPDH ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĖą╝ą┐čāą╗čīčü presence, ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÅ čüąĖą│ąĮą░ą╗ ą║ ą╗ąŠą│. 0 ąĮą░ ą▓čĆąĄą╝čÅ tPDL. ąöą╗čÅ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüą░ presence ą╝ą░čüč鹥čĆ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą╗ąŠą│ąĖč湥čüą║ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ čłąĖąĮčŗ 1-Wire ą▓ ą╝ąŠą╝ąĄąĮčé tMSP.

ą×ą║ąĮąŠ ą▓čĆąĄą╝ąĄąĮąĖ tRSTH ą┤ąŠą╗ąČąĮąŠ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▒čŗčéčī čüčāą╝ą╝ąŠą╣ tPDHMAX, tPDLMAX ąĖ tRECMIN. ąĪčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąĖčüč鹥č湥ąĮąĖčÅ tRSTH čćąĖą┐ DS2431 ą│ąŠč鹊ą▓ ą║ ąŠą▒ą╝ąĄąĮčā ą┤ą░ąĮąĮčŗą╝ąĖ. ąÆ čüąĄčéąĖ čüąŠ čüą╝ąĄčłą░ąĮąĮčŗą╝ ąĮą░čüąĄą╗ąĄąĮąĖąĄą╝ (ą║ąŠą│ą┤ą░ ą║ čłąĖąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆą░ąĘąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓) tRSTH ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░čüčłąĖčĆąĄąĮ ą┤ąŠ ą╝ąĖąĮąĖą╝čāą╝ 480 ą╝ą║čü ą┐čĆąĖ čüą║ąŠčĆąŠčüčéąĖ standard ąĖ 48 ą╝ą║čü ą┐čĆąĖ čüą║ąŠčĆąŠčüčéąĖ overdrive ą┤ą╗čÅ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ ą┤čĆčāą│ąĖčģ 1-Wire čāčüčéčĆąŠą╣čüčéą▓.

ąĀąĖčü. 10. ą¤čĆąŠčåąĄą┤čāčĆą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ: ąĖą╝ą┐čāą╗čīčü Reset ąĖ ąĖą╝ą┐čāą╗čīčü Presence.

[ąĪą╗ąŠčéčŗ ą▓čĆąĄą╝ąĄąĮąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ]

ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čü DS2431 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ą░čģ ą▓čĆąĄą╝ąĄąĮąĖ (čéą░ą╣ą╝-čüą╗ąŠčéą░čģ), ą║ą░ąČą┤čŗą╣ ąĖąĘ ą║ąŠč鹊čĆčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčé ąŠą┤ąĖąĮ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. Write-čüą╗ąŠčé ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąŠčé master ą║ slave (Master-to-Slave). Read-čüą╗ąŠčé ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąŠčé slave ą║ master (Slave-to-Master). ąĀąĖčü. 11 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓ ąĘą░ą┐ąĖčüąĖ (write) ąĖ čćč鹥ąĮąĖčÅ (read).

ąĀąĖčü. 11. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (Read/Write).

ąÆčüąĄ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ ąĮą░čćąĖąĮą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ master ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčé ą╗ąĖąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ ą║ ą╗ąŠą│. 0. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą╗ąĖąĮąĖąĖ 1-Wire čāą┐ą░ą┤ąĄčé ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ VTL, čćąĖą┐ DS2431 ąĘą░ą┐čāčüčéąĖčé čüą▓ąŠą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓, ą║ąŠč鹊čĆčŗą╣ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ąŠą│ą┤ą░ ą╗ąĖąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ write-čüą╗ąŠčéą░, ąĖ ą║ą░ą║ ą┤ąŠą╗ą│ąŠ ą┤ą░ąĮąĮčŗąĄ ąŠčüčéą░čÄčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ read-čüą╗ąŠčéą░.

Master-to-Slave. ąöą╗čÅ čéą░ą╣ą╝-čüą╗ąŠčéą░ ąĘą░ą┐ąĖčüąĖ ąĄą┤ąĖąĮąĖčåčŗ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą╗ąĖąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą▓čŗčüąĖčéčī ą┐ąŠčĆąŠą│ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ VTH ą┤ąŠ ąĖčüč鹥č湥ąĮąĖčÅ tW1LMAX ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐ąĖčüąĖ. ąöą╗čÅ čéą░ą╣ą╝-čüą╗ąŠčéą░ ąĘą░ą┐ąĖčüąĖ ąĮčāą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą╗ąĖąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠą╗ąČąĮąŠ ąŠčüčéą░ą▓ą░čéčīčüčÅ ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ VTH ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ąĖčüč鹥č湥čé tW0LMIN ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐ąĖčüąĖ. ąöą╗čÅ ąĮą░ąĖą▒ąŠą╗ąĄąĄ ąĮą░ą┤ąĄąČąĮąŠą╣ čüą▓čÅąĘąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą▓čŗčłą░čéčī VILMAX ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą│ąŠ ąŠą║ąĮą░ tW0L ąĖą╗ąĖ tW1L. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠčĆąŠą│ VTH ą▒čŗą╗ ą┐čĆąĄąŠą┤ąŠą╗ąĄąĮ, čćąĖą┐čā DS2431 čéčĆąĄą▒čāąĄčéčüčÅ ą▓čĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ tREC, ą┐čĆąĄąČą┤ąĄ č湥ą╝ ąŠąĮ ą▒čāą┤ąĄčé ą│ąŠč鹊ą▓ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā čéą░ą╣ą╝-čüą╗ąŠčéčā.

Slave-to-Master. ąĪą╗ąŠčé čćč鹥ąĮąĖčÅ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą║ą░ą║ čüą╗ąŠčé ąĘą░ą┐ąĖčüąĖ ąĄą┤ąĖąĮąĖčåčŗ. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠą╗ąČąĮąŠ ąŠčüčéą░ą▓ą░čéčīčüčÅ ąĮąĖąČąĄ VTL ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ąĖčüč鹥č湥čé ą▓čĆąĄą╝čÅ tRL čüčćąĖčéčŗą▓ą░ąĮąĖčÅ. ąÆąŠ ą▓čĆąĄą╝čÅ ąŠą║ąĮą░ tRL, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ DS2431 ąŠčéą▓ąĄčćą░ąĄčé ą▒ąĖč鹊ą╝ 0, ąŠąĮąŠ ąĮą░čćąĖąĮą░ąĄčé ą┐ąŠą┤čéčÅą│ąĖą▓ą░čéčī ą╗ąĖąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ ą║ ą╗ąŠą│. 0; ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čćąĖą┐ą░ DS2431 ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ č鹊, ą║ąŠą│ą┤ą░ čŹčéą░ ą┐ąŠą┤čéčÅąČą║ą░ ąĘą░ą║ąŠąĮčćąĖčéčüčÅ, ąĖ čāčĆąŠą▓ąĄąĮčī ą▓ąĄčĆąĮąĄčéčüčÅ ą║ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ DS2431 ąŠčéą▓ąĄčćą░ąĄčé ą▒ąĖč鹊ą╝ 1, ąŠąĮąŠ ą▓ąŠąŠą▒čēąĄ ąĮąĄ čāą┤ąĄčƹȹĖą▓ą░ąĄčé ą╗ąĖąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ, ąŠčüčéą░ą▓ą╗čÅčÅ ąĄčæ ą▓ ą╗ąŠą│. 1, ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüčĆą░ąĘčā ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą║ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗ą░ tRL.

ąĪčāą╝ą╝ą░ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ tRL + ╬┤ (ą▓čĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ) ąĮą░ ąŠą┤ąĮąŠą╣ čüč鹊čĆąŠąĮąĄ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ DS2431 ąĮą░ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą│ą╗ą░ą▓ąĮąŠąĄ ąŠą║ąĮąŠ ą▓čŗą▒ąŠčĆą║ąĖ (tMSRMIN - tMSRMAX), ą▓ ą║ąŠč鹊čĆąŠą╝ ą╝ą░čüč鹥čĆ ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüčćąĖčéčŗą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ. ąöą╗čÅ ąĮą░ąĖą▒ąŠą╗ąĄąĄ ąĮą░ą┤ąĄąČąĮąŠą╣ čüą▓čÅąĘąĖ tRL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮą░čüč鹊ą╗čīą║ąŠ ą║ąŠčĆąŠčéą║ąĖą╝, ąĮą░čüą║ąŠą╗čīą║ąŠ čŹč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠ, ąĖ ą╝ą░čüč鹥čĆ ą┤ąŠą╗ąČąĄąĮ čćąĖčéą░čéčī ą▒ą╗ąĖąĘą║ąŠ, ąĮąŠ ąĮąĄ ą┐ąŠąĘą┤ąĮąĄąĄ tMSRMAX. ą¤ąŠčüą╗ąĄ čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ą╝ą░čüč鹥čĆ ą┤ąŠą╗ąČąĄąĮ ą┤ąŠąČą┤ą░čéčīčüčÅ ąĖčüč鹥č湥ąĮąĖčÅ čüčĆąŠą║ą░ ą┤ąĄą╣čüčéą▓ąĖčÅ tSLOT. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą▓čĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ tREC ą┤ą╗čÅ ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ąĖ DS2431 ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą▓čĆąĄą╝ąĄąĮąĮąŠą╝čā ąĖąĮč鹥čĆą▓ą░ą╗čā. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 tREC, čāą║ą░ąĘą░ąĮąĮčŗą╣ ąĘą┤ąĄčüčī, ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ ąŠą┤ąĮąŠą╝čā DS2431, ą┐čĆąĖą║čĆąĄą┐ą╗ąĄąĮąĮąŠą╝čā ą║ ą╗ąĖąĮąĖąĖ 1-Wire. ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ tREC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░čüčłąĖčĆąĄąĮ ą┤ą╗čÅ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ą▓čģąŠą┤ąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ 1-Wire čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆ ą║ą░č湥čüčéą▓ąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓čŗ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčé ą░ą║čéąĖą▓ąĮčŗą╣ pullup ą▓ č鹥č湥ąĮąĖąĄ 1-Wire ą▓čĆąĄą╝ąĄąĮąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ, čéą░ą║ąŠą╣ ą║ą░ą║ 1-Wire ą╗ąĖąĮąĄą╣ąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ DS2482-x00 ąĖą╗ąĖ DS2480B.

[ąŻą╗čāčćčłąĄąĮąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąĄčéąĖ (ą│ąĖčüč鹥čĆąĄąĘąĖčü č鹊čćą║ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ)]

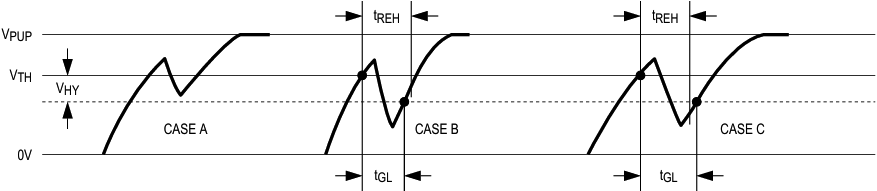

ąÆ čĆą░ą▒ąŠč湥ą╝ čäąĖąĘąĖč湥čüą║ąŠą╝ ąŠą║čĆčāąČąĄąĮąĖąĖ 1-Wire č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╗ąĖąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠ č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠą▓, ą║ąŠąĮčéčĆąŠą╗ąĖčĆčāąĄą╝čŗčģ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ (1-Wire ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝). ą¤ąŠčŹč鹊ą╝čā 1-Wire čüąĄčéąĖ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗ ą║ čłčāą╝čā čĆą░ąĘą╗ąĖčćąĮąŠą│ąŠ ą┐čĆąŠąĖčüčģąŠąČą┤ąĄąĮąĖčÅ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čäąĖąĘąĖč湥čüą║ąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░ ąĖ č鹊ą┐ąŠą╗ąŠą│ąĖąĖ čüąĄčéąĖ ąŠčéčĆą░ąČąĄąĮąĖčÅ ąŠčé ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ ąĖ č鹊č湥ą║ ąŠčéą▓ąĄčéą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą│čāčé ą▓ ąĮąĄą║ąŠč鹊čĆąŠą╣ čüč鹥ą┐ąĄąĮąĖ čüą║ą╗ą░ą┤čŗą▓ą░čéčīčüčÅ ąĖą╗ąĖ ąŠčéą╝ąĄąĮčÅčéčī čāčĆąŠą▓ąĮąĖ ą┤čĆčāą│ ą┤čĆčāą│ą░. ąóą░ą║ąĖąĄ ąŠčéčĆą░ąČąĄąĮąĖčÅ ą▓ąĖą┤ąĮčŗ ą║ą░ą║ ą│ą╗čÄą║ąĖ ąĖą╗ąĖ ąĘą▓ąŠąĮ ąĮą░ 1-Wire ą╗ąĖąĮąĖąĖ čüą▓čÅąĘąĖ. ą©čāą╝, ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╣ ąĮą░ ą╗ąĖąĮąĖčÄ 1-Wire ąŠčé ą▓ąĮąĄčłąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓, čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ čüą▒ąŠčÄ čüąĖą│ąĮą░ą╗ą░. ąĪą▒ąŠą╣ ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮą░čĆą░čüčéą░čÄčēąĄą│ąŠ čäčĆąŠąĮčéą░ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ č鹊ą╝čā, čćč鹊 ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠč鹥čĆčÅąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ čü ą▓ąĄą┤čāčēąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ąĖ ą║ą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ą║ąŠą╝ą░ąĮą┤ą░ Search ROM ąŠą║ą░ąČąĄčéčüčÅ ą▓ čéčāą┐ąĖą║ąĄ ąĖą╗ąĖ ą║ąŠą╝ą░ąĮą┤ą░ čäčāąĮą║čåąĖąĖ, čüą┐ąĄčåąĖčäąĖčćąĮąŠą╣ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ą░, ą▒čāą┤ąĄčé ą┐čĆąĄčĆą▓ą░ąĮą░. ąöą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓ čüąĄč鹥ą▓čŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ DS2431 ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĮąŠą▓čŗą╣ čäčĆąŠąĮčé-菹Įą┤ 1-Wire, čćč鹊 ą┤ąĄą╗ą░ąĄčé ąĄą│ąŠ ą╝ąĄąĮąĄąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗą╝ ą║ čłčāą╝čā.

ążčĆąŠąĮčé-菹Įą┤ DS2431 1-Wire ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗčģ slave-čāčüčéčĆąŠą╣čüčéą▓ čéčĆąĄą╝čÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ąĖ.

1) ąśą╝ąĄąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąĮąĖąĘą║ąŠčćą░čüč鹊čéąĮą░čÅ čäąĖą╗čīčéčĆą░čåąĖčÅ ą▓ čüčģąĄą╝ąĄ, ą║ąŠč鹊čĆą░čÅ ąŠą▒ąĮą░čĆčāąČąĖą▓ą░ąĄčé čäčĆąŠąĮčé ą┐ą░ą┤ąĄąĮąĖčÅ ą▓ ąĮą░čćą░ą╗ąĄ čéą░ą╣ą╝-čüą╗ąŠčéą░. ąŁč鹊 čüąĮąĖąČą░ąĄčé čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗą╝ čłčāą╝ą░ą╝. ąŁčéą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ čäąĖą╗čīčéčĆą░čåąĖčÅ ąĮąĄ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ overdrive.

2) ąśą╝ąĄąĄčé ą╝ąĄčüč鹊 ą│ąĖčüč鹥čĆąĄąĘąĖčü ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ ą┐ąŠčĆąŠą│ą░ VTH ąŠčé 0 ą║ 1. ąĢčüą╗ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą┐ą░čĆą░ąĘąĖčéąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ą┐ąĄčĆąĄčüąĄą║ą░ąĄčé VTH, ąĮąŠ ąĮąĄ ąŠą┐čāčüą║ą░ąĄčéčüčÅ ąĮąĖąČąĄ VTH - VHY, ąŠąĮ ąĮąĄ čĆą░čüą┐ąŠąĘąĮą░ąĄčéčüčÅ (čĆąĖčü. 12, čüą╗čāčćą░ą╣ CASE A). ąōąĖčüč鹥čĆąĄąĘąĖčü čŹčäč乥ą║čéąĖą▓ąĄąĮ ą┐čĆąĖ ą╗čÄą▒ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ 1-Wire.

3) ąĪčāčēąĄčüčéą▓čāąĄčé ą▓čĆąĄą╝ąĄąĮąĮąŠąĄ ąŠą║ąĮąŠ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ąŠąĄ ą▓čĆąĄą╝ąĄąĮąĄą╝ čāą┤ąĄčƹȹ░ąĮąĖčÅ tREH ą┐ąĄčĆąĄą┤ąĮąĄą│ąŠ čäčĆąŠąĮčéą░, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ čüą▒ąŠąĖ ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠąĮąĖ ą▓čŗčģąŠą┤čÅčé ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ VTH - VHY (čĆąĖčü. 12, čüą╗čāčćą░ą╣ CASE B, tGL < tREH). ąōą╗čāą▒ąŠą║ąĖąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĖą╗ąĖ ą│ą╗čÄą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ą┐ąŠąĘą┤ąĮąŠ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ ą┐ąŠčĆąŠą│ą░ VTH ąĖ ą▓čŗčģąŠą┤čÅčé ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ąŠą║ąĮą░ tREH, ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮčŗ ąĖ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĘą░ ąĮą░čćą░ą╗ąŠ ąĮąŠą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ (čĆąĖčü. 12, čüą╗čāčćą░ą╣ CASE C, tGL Ōēź tREH).

ąĀąĖčü. 12. ąĪčģąĄą╝ą░ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ čłčāą╝ą░.

ąŻčüčéčĆąŠą╣čüčéą▓ą░, ąĖą╝ąĄčÄčēąĖąĄ čāą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čüą▓ąŠąĖčģ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░čģ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ VHY ąĖ tREH, ąĖčüą┐ąŠą╗čīąĘčāčÄčé čāčüąŠą▓ąĄčĆčłąĄąĮčüčéą▓ąŠą▓ą░ąĮąĮčŗą╣ 1-Wire front-end.

[ąōąĄąĮąĄčĆą░čåąĖčÅ CRC]

DS2431 ąĖčüą┐ąŠą╗čīąĘčāąĄčé 2 čĆą░ąĘąĮčŗčģ čéąĖą┐ą░ ą║ąŠąĮčéčĆąŠą╗čīąĮčŗčģ čüčāą╝ą╝ CRC. ą×ą┤ąĮą░ ąĖąĘ ąĮąĖčģ 8-ą▒ąĖčéąĮą░čÅ, ąĖ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čüą░ą╝ąŠą╝ čüčéą░čĆčłąĄą╝ ąĘąĮą░čćą░čēąĄą╝ ą▒ą░ą╣č鹥 64-ą▒ąĖčé ROM-ą║ąŠą┤ą░. ą£ą░čüč鹥čĆ čłąĖąĮčŗ ą╝ąŠąČąĄčé ą▓čŗčćąĖčüą╗ąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ CRC ąŠčé ą┐ąĄčĆą▓čŗčģ 56 ą▒ąĖčé ąŠčé 64-ą▒ąĖčéąĮąŠą│ąŠ ROM-ą║ąŠą┤ą░ ąĖ čüčĆą░ą▓ąĮąĖčéčī ą▓čŗčćąĖčüą╗ąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╝ ą▓ DS2431, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čćč鹊 čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ROM ą┐čĆąŠčłą╗ąŠ ą▒ąĄąĘ ąŠčłąĖą▒ąŠą║. ąŁą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ čäčāąĮą║čåąĖčÅ ą┐ąŠą╗ąĖąĮąŠą╝ą░ čā čŹč鹊ą╣ CRC: X8 + X5 + X4 + 1. ąŁčéą░ 8-ą▒ąĖčéąĮą░čÅ CRC ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ ą▓ true-č乊čĆą╝ąĄ (ą▒ąĄąĘ ąĖąĮą▓ąĄčĆčüąĖąĖ). ą×ąĮą░ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ ąĖ ą┐čĆąŠčłąĖą▓ą░ąĄčéčüčÅ ą▓ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ROM-ą║ąŠą┤ą░.

ąöčĆčāą│ą░čÅ CRC 16-ą▒ąĖčéąĮą░čÅ, ąŠąĮą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéąĖąĘąŠą▓ą░ąĮąĮąŠą╣ čäčāąĮą║čåąĖąĖ CRC-16 ą┐ąŠą╗ąĖąĮąŠą╝ą░ X16 + X15 + X2 + 1. ąŁčéą░ CRC ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▒čŗčüčéčĆąŠą╣ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ą▓ scratchpad ąĖą╗ąĖ čćč鹥ąĮąĖąĖ ąĖąĘ scratchpad. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé 8-ą▒ąĖčéąĮąŠą╣ CRC čŹčéą░ 16-ą▒ąĖčéąĮą░čÅ CRC ą▓čüąĄą│ą┤ą░ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą▓ ąĖąĮą▓ąĄčĆčüąĮąŠą╣ č乊čĆą╝ąĄ. CRC-ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░ DS2431 (čĆąĖčü. 13) ą▓čŗčćąĖčüą╗čÅąĄčé ąĮąŠą▓čāčÄ 16-ą▒ąĖčéąĮčāčÄ CRC, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą║ąŠą╝ą░ąĮą┤čŗ (čĆąĖčü. 7). ą£ą░čüč鹥čĆ čłąĖąĮčŗ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ CRC, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝, ą▓čŗčćąĖčüą╗ąĄąĮąĮčŗą╝ ą┐ąŠ ą┤ą░ąĮąĮčŗą╝, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī - ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ą╗ąĖ ąŠą┐ąĄčĆą░čåąĖčÄ ąĖą╗ąĖ ąĘą░ąĮąŠą▓ąŠ ą┐ąĄčĆąĄčćąĖčéą░čéčī ą┐ąŠčĆčåąĖčÄ ą┤ą░ąĮąĮčŗčģ ą▓ čüą╗čāčćą░ąĄ ąŠčłąĖą▒ą║ąĖ CRC.

ąĀąĖčü. 13. ą×ą┐ąĖčüą░ąĮąĖąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ąĖ ą┐ąŠą╗ąĖąĮąŠą╝ą░ CRC-16.

ąĪ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Write Scratchpad ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ CRC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čāč鹥ą╝ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ąŠčćąĖčüčéą║ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ CRC, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą▓ą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ, čåąĄą╗ąĄą▓čŗąĄ ą░ą┤čĆąĄčüą░ TA1 ąĖ TA2, ąĖ ą▓čüąĄ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ, ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ. DS2431 ą┐ąĄčĆąĄą┤ą░ąĄčé čŹčéčā CRC č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ E[2:0] = 111b.

ąĪ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Read Scratchpad ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ CRC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čāč鹥ą╝ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ąŠčćąĖčüčéą║ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ CRC, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą▓ą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ, čåąĄą╗ąĄą▓čŗąĄ ą░ą┤čĆąĄčüą░ TA1 ąĖ TA2, ą▒ą░ą╣čé E/S ąĖ ą┤ą░ąĮąĮčŗąĄ scratchpad, ą║ą░ą║ ąŠąĮąĖ ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ čćąĖą┐ąŠą╝ DS2431. DS2431 ą┐ąĄčĆąĄą┤ą░ąĄčé čŹčéčā CRC č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čćč鹥ąĮąĖąĄ čćč鹥ąĮąĖąĄ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ čćč鹥ąĮąĖčÅ scratchpad. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą│ąĄąĮąĄčĆą░čåąĖąĖ CRC čüą╝. ą░ą┐ąĮąŠčāčé 27 [4].

ąøąĄą│ąĄąĮą┤ą░ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąŠąĮąĮąŠą│ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ 1-Wire, čüą┐ąĄčåąĖčäąĖčćąĮą░čÅ ą┤ą╗čÅ ą║ąŠą╝ą░ąĮą┤:

| ąĪąśą£ąÆą×ąø |

ą×ą¤ąśąĪąÉąØąśąĢ |

| RST |

ąśą╝ą┐čāą╗čīčü čüą▒čĆąŠčüą░ (1-Wire reset pulse), ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╣ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ. |

| PD |

ąśą╝ą┐čāą╗čīčü ą┐čĆąĖčüčāčéčüčéą▓ąĖčÅ (1-Wire presence pulse) ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╣ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. |

| Select |

ąÜąŠą╝ą░ąĮą┤ą░ ąĖ ą┤ą░ąĮąĮčŗąĄ, čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčēąĖąĄ ą┐čĆąŠč鹊ą║ąŠą╗čā čäčāąĮą║čåąĖą╣ ROM. |

| WS |

ąÜąŠą╝ą░ąĮą┤ą░ "Write Scratchpad". |

| RS |

ąÜąŠą╝ą░ąĮą┤ą░ "Read Scratchpad". |

| CPS |

ąÜąŠą╝ą░ąĮą┤ą░ "Copy Scratchpad". |

| RM |

ąÜąŠą╝ą░ąĮą┤ą░ "Read Memory". |

| TA |

ą”ąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü (Target address) TA1, TA2. |

| TA-E/S |

ą”ąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü TA1, TA2 čü ą▒ą░ą╣č鹊ą╝ E/S. |

| < 8ŌĆōT[2:0] bytes> |

ą¤ąĄčĆąĄą┤ą░čćą░ čéą░ą║ąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé, čüą║ąŠą╗čīą║ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ą╗čÅ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą║ąŠąĮčåą░ scratchpad ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ čåąĄą╗ąĄą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░. |

| < Data to EOM> |

ą¤ąĄčĆąĄą┤ą░čćą░ čéą░ą║ąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé, čüą║ąŠą╗čīą║ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ąŠ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą║ąŠąĮčåą░ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░. |

| CRC-16 |

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖąĮą▓ąĄčĆčüąĮąŠą╣ CRC-16. |

| FF Loop |

ąØąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čåąĖą║ą╗, ą▓ ą║ąŠč鹊čĆąŠą╝ ą╝ą░čüč鹥čĆ čüčćąĖčéčŗą▓ą░ąĄčé ą▒ą░ą╣čéčŗ FF. |

| AA Loop |

ąØąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čåąĖą║ą╗, ą▓ ą║ąŠč鹊čĆąŠą╝ ą╝ą░čüč鹥čĆ čüčćąĖčéčŗą▓ą░ąĄčé ą▒ą░ą╣čéčŗ AA. |

| Programming |

ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ EEPROM; ą▓ąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą│ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ čłąĖąĮąĄ 1-Wire. |

ą”ą▓ąĄč鹊ą▓čŗąĄ ą║ąŠą┤čŗ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąŠąĮąĮąŠą│ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ 1-Wire:

| Master ŌåÆ Slave |

Slave ŌåÆ Master |

Programming |

ą¤čĆąĖą╝ąĄčĆčŗ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖą╣ 1-Wire

Write Scratchpad (ąŠčłąĖą▒ą║ąĖ ą▒čŗčéčī ąĮąĄ ą╝ąŠąČąĄčé):

| RST |

PD |

Select |

WS |

TA |

< 8ŌĆōT[2:0] bytes> |

CRC-16 |

FF Loop |

Read Scratchpad (ąŠčłąĖą▒ą║ąĖ ą▒čŗčéčī ąĮąĄ ą╝ąŠąČąĄčé):

| RST |

PD |

Select |

RS |

TA-E/S |

< 8ŌĆōT[2:0] bytes> |

CRC-16 |

FF Loop |

Copy Scratchpad (čāčüą┐ąĄčģ):

| RST |

PD |

Select |

CPS |

TA-E/S |

Programming |

AA Loop |

Copy Scratchpad (ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą░ą┤čĆąĄčü, ąĖą╗ąĖ PF = 1, ąĖą╗ąĖ Copy Protected):

| RST |

PD |

Select |

CPS |

TA-E/S |

FF Loop |

Read Memory (čāčüą┐ąĄčģ):

| RST |

PD |

Select |

RM |

TA |

< Data to EOM> |

FF Loop |

Read Memory (ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą░ą┤čĆąĄčü):

| RST |

PD |

Select |

RM |

TA |

FF Loop |

[ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čäčāąĮą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ]

ąŚą░ą┐ąĖčüčī ą┐ąĄčĆą▓čŗčģ 8 ą▒ą░ą╣čé ąĮą░ čüčéčĆą░ąĮąĖčåčā ą┐ą░ą╝čÅčéąĖ 1. ą¦č鹥ąĮąĖąĄ ą▓čüąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąÜąŠą│ą┤ą░ ą║ ą╝ą░čüč鹥čĆčā čłąĖąĮčŗ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ DS2431, ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖčÅ ą╝ąŠąČąĄčé ą▓čŗą│ą╗čÅą┤ąĄčéčī čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

| ąĀąĄąČąĖą╝ MASTER |

DATA (LSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝) |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ |

| Tx |

(Reset) |

ąśą╝ą┐čāą╗čīčü čüą▒čĆąŠčüą░ (reset) |

| Rx |

(Presence) |

ąśą╝ą┐čāą╗čīčü ą┐čĆąĖčüčāčéčüčéą▓ąĖčÅ (presence) |

| Tx |

CCh |

ąÜąŠą╝ą░ąĮą┤ą░ Skip ROM |

| Tx |

0Fh |

ąÜąŠą╝ą░ąĮą┤ą░ Write Scratchpad |

| Tx |

20h |

TA1, ąĮą░čćą░ą╗čīąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ 20h |

| Tx |

00h |

TA2, ą░ą┤čĆąĄčü = 0020h |

| Tx |

< 8 Data Bytes> |

ąŚą░ą┐ąĖčüčī 8 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą▓ scratchpad |

| Rx |

< 2 Bytes CRC-16> |

ą¦č鹥ąĮąĖąĄ CRC ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ čåąĄą╗ąŠčüčéąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ |

| Tx |

(Reset) |

ąśą╝ą┐čāą╗čīčü čüą▒čĆąŠčüą░ |

| Rx |

(Presence) |

ąśą╝ą┐čāą╗čīčü ą┐čĆąĖčüčāčéčüčéą▓ąĖčÅ |

| Tx |

CCh |

ąÜąŠą╝ą░ąĮą┤ą░ Skip ROM |

| Tx |

AAh |

ąÜąŠą╝ą░ąĮą┤ą░ Read Scratchpad |

| Rx |

20h |

ą¦č鹥ąĮąĖąĄ TA1, ąĮą░čćą░ą╗čīąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ 20h |

| Rx |

00h |

ą¦č鹥ąĮąĖąĄ TA2, ą░ą┤čĆąĄčü = 0020h |

| Rx |

07h |

ą¦č鹥ąĮąĖąĄ E/S, ą║ąŠąĮąĄčćąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ = 111b, AA, PF = 0 |

| Rx |

< 8 Data Bytes> |

ą¦č鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ scratchpad ąĖ ą┐čĆąŠą▓ąĄčĆą║ą░ |

| Rx |

< 2 Bytes CRC-16> |

ą¦č鹥ąĮąĖąĄ CRC ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ čåąĄą╗ąŠčüčéąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ |

| Tx |

(Reset) |

ąśą╝ą┐čāą╗čīčü čüą▒čĆąŠčüą░ |

| Rx |

(Presence) |

ąśą╝ą┐čāą╗čīčü ą┐čĆąĖčüčāčéčüčéą▓ąĖčÅ |

| Tx |

CCh |

ąÜąŠą╝ą░ąĮą┤ą░ Skip ROM |

| Tx |

55h |

ąÜąŠą╝ą░ąĮą┤ą░ Copy Scratchpad |

| Tx |

20h |

TA1 (ą║ąŠą┤ ą░ą▓č鹊čĆąĖąĘą░čåąĖąĖ) |

| Tx |

00h |

TA2 (ą║ąŠą┤ ą░ą▓č鹊čĆąĖąĘą░čåąĖąĖ) |

| Tx |

07h |

E/S (ą║ąŠą┤ ą░ą▓č鹊čĆąĖąĘą░čåąĖąĖ) |

| - |

< 1-Wire Idle High> |

ą×ąČąĖą┤ą░ąĮąĖąĄ tPROGMAX ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čäčāąĮą║čåąĖąĖ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ |

| Rx |

AAh |

ą¦č鹥ąĮąĖąĄ čüčéą░čéčāčüą░ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ, AAh = čāčüą┐ąĄčģ |

| Tx |

(Reset) |

ąśą╝ą┐čāą╗čīčü čüą▒čĆąŠčüą░ |

| Rx |

(Presence) |

ąśą╝ą┐čāą╗čīčü ą┐čĆąĖčüčāčéčüčéą▓ąĖčÅ |

| Tx |

CCh |

ąÜąŠą╝ą░ąĮą┤ą░ Skip ROM |

| Tx |

F0h |

ąÜąŠą╝ą░ąĮą┤ą░ Read Memory |

| Tx |

00h |

TA1, ąĮą░čćą░ą╗čīąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ = 00h |

| Tx |

00h |

TA2, ą░ą┤čĆąĄčü = 0000h |

| Rx |

< 144 Data Bytes> |

ą¦č鹥ąĮąĖąĄ ą▓čüąĄą│ąŠ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ |

| Tx |

(Reset) |

ąśą╝ą┐čāą╗čīčü čüą▒čĆąŠčüą░ |

| Rx |

(Presence) |

ąśą╝ą┐čāą╗čīčü ą┐čĆąĖčüčāčéčüčéą▓ąĖčÅ |

[ąĪčüčŗą╗ą║ąĖ]

1. DS2431 EEPROM.

2. Understanding and Using Cyclic Redundancy Checks with Maxim 1-Wire and iButton Products site:analog.com.

3. 1-Wire Search Algorithm site:analog.com.

4. Application Note 27 Understanding and Using Cyclic Redundancy Checks with Dallas Semiconductor iButtonŌäó Products site:microshadow.com. |