# **UAA2022**

#### 16 SEGMENT LED DRIVER

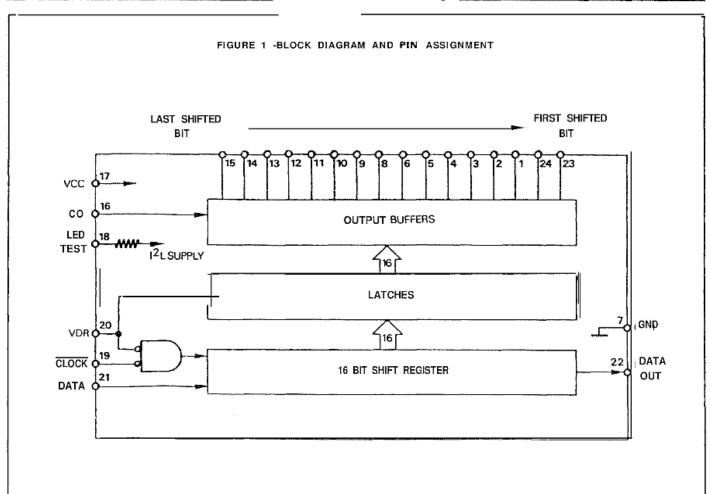

The UAA2022 is a 16-bit serial data input to a 16-segment LED driver. Brightness control of common anode LED's from an external control voltage is possible. The UAA2022 is particularly suitable for Hi-Fi applications and is implemented in I<sup>2</sup>L linear technology.

- · LED brightness control voltage

- Current source Segment driver Outputs

- No external resistors for Segment currents

- Non-multiplexed, therefore no RFI ,

- Cascadable

#### 16 SEGMENT LED DRIVER

SILICON MONOLITHIC INTEGRATED CIRCUIT

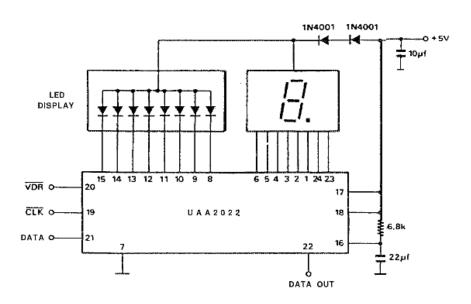

FIGURE 4 - TYPICAL APPLICATION

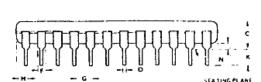

#### **OUTLINE DIMENSIONS**

P SUF FIX PLASTIC PACKAGE CASE 724

1. LEADS, TAUE POSITIONED WITHIN 0.25 mrn (0.010) OIA ATSEATING PLANE AT MAXIMUM MATERIAL CONDITION (DIM. "O")

| DIM          | MILLIMETERS  |              | INCHES    |       |  |

|--------------|--------------|--------------|-----------|-------|--|

|              | MIN          | MAX          | MIN       | MAX   |  |

| A            | 31.24        | 32.13        | 1.260     | 1.285 |  |

| 8            | 6.10         | 6.60         | 0.240     | 0.260 |  |

| C            | 4.06         | 4.57         | 0.160     | 0.180 |  |

| 0            | 0.38         | 0.51         | 0.015     | 0.020 |  |

| F            | 1.02         | 1.52         | 0.040     | 0.060 |  |

| G            | 2.54 BSC     |              | 0.100 BSC |       |  |

| н            | 1.60         | 2.11         | 0.063     | 0.083 |  |

|              |              |              |           |       |  |

| ı            | 0.18         | 0.30         | 0.007     | 0.012 |  |

| - <u>K</u> - | 0.18<br>2.92 | 0.30<br>3.43 | 0.007     | 0.012 |  |

|              |              |              |           |       |  |

| K            | 2.92         | 3.43         | 0.115     | 0.135 |  |

This information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the apptication or use of any product or circuit described herein. No license is conveyed under patent rights in any form. When this document contains information on a new product, specifications herein are subject to change without notice.

## **MOTOROLA** Semiconductor Products Inc.

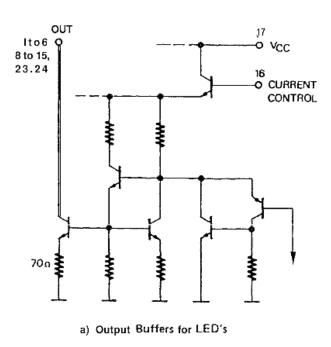

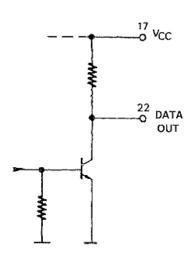

FIGURE 2 - CIRCUIT CONFIGURATIONS

b) Output Stage of Data Output

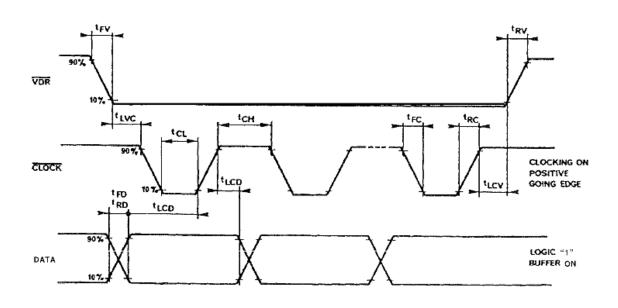

FIGURE 3 -DEFINITION OF SWITCHING TIMES

MOTOROLA Semiconductor Products Inc.

#### CIRCUIT DESCRIPTION

he UAA2022 is intended to control common anode ED's and allows brightness Variation from an external partrol voltage. Since it is not multiplexed it is particularly lited for hi-fi applications etc.

the circuit receives 16 bit serial data by means of the igital inputs VDR (chip select), Clock and Data (TTL-vels). The information is fed into a shift-register, and men is stored in latches which in turn control the output uffers. These output buffers (segment drivers) have urrent source characteristics (see figure 2a), thus no xternal resitors are needed to set up the Segment currents for 100 % luminosity).

figure 3 shows the timing diagram of the circuit. On the regative going VOR-edge the latches are disconnected

from the shift register and new information is shifted in. On the positive VDR-edge the latches are reconnected, thus transferring new information to the Outputs. (See f igure 2a.)

The shift register also has a data output. (See figure 2b.) This allows the microprocessor to pass data through the UAA 2022, and thus drive further circuits from the same data and chip-select pins. The UAA 2022 shifts and Outputs data on the positive going clock edge. Thus for reliable data transfer, it has to be the first circuit in the line, when connected in series with circuits which shift on the negative going clock edge. The circuit is cascadable and can be cascaded with the UAA2000 and UAA2001/2010.

#### INPUT/OUTPUT FUNCTIONS

3UFFER OUTPUTS - (pins 1 to 6, 8 to 15, 23, 24)

These Outputs have current source characteristics to drive the LED segments without external resistances.

CURRENT CONTROL - (pin 16)

Serves to vary the output currents of the buffers. This pin has to be connected to VCC (pin 17) for maximum imminosity. The buffer currents decrease linearly with the control voltage, going down to zero at about 2V.

LED - TEST - (pin 18)

This pin supplies the logic section of the circuit, when connected to ground all output buffers are switched on.

CLPCK -- (pin 19)

Thrs pin delivers the clock signal to the shift register,

which accepts shifts and Outputs data on the positive going edge. It should be noted that within the  $\overline{\text{VDR}}$ -window, when  $\overline{\text{VDR}}$  is low, the clock has to be high at the beginning and the end of the clock pulse train.

VDR .- (pin 20)

This pin is the chip select and is active when low.

DATA - (pin 2 1)

Data is entered into the device serially via this pin and passed directly into the shift register- In turn, this controls the latches and output buffers. (Logic "1" = Buffer ON)

DATA OUT - (pin 22)

Is the data output of the shift register- Allows cascading with circuits operating on the same VDR and clock signals.

## ELECTRICAL CHARACTERISTICS (VCC=5V, TA=25°C)

| Characteristic                                  | Pin            | Symbol           | Min  | Тур | Max             | Unit |

|-------------------------------------------------|----------------|------------------|------|-----|-----------------|------|

| Logic Input Levels, VDR, Clock, Data            | 19, 20, 21     | V <sub>LOG</sub> |      |     |                 |      |

| Low State                                       |                |                  | 0    |     | 8.0             | ٧    |

| High State                                      |                |                  | 2    |     | 6               | V    |

| Logic Input Currents                            |                | LOG              |      |     |                 |      |

| Low State                                       |                |                  |      |     | - 100           | μА   |

| High State                                      | ļ              |                  |      |     | 10              | μА   |

| Control Voltage Range 1)                        | 16             | v <sub>co</sub>  | 0    |     | v <sub>cc</sub> |      |

| Supply Voltage                                  | 17             | v <sub>cc</sub>  | 4,5  |     | 5.5             | V    |

| Control Current                                 | 16             | ¹co              |      |     | 1               | mA   |

| Control Voltage, LED Test                       | 18             | VLE              |      |     |                 |      |

| Low Level (no Logic Supply, all Buffers ON)     |                |                  | 0    |     | 0.5             | V    |

| High Level (normal Operation)                   |                |                  | 4.50 |     | V <sub>CC</sub> |      |

| Data Out (figure 2)                             |                |                  |      |     |                 |      |

| Output Voltage, Logic "0" (1mA)                 | V <sub>D</sub> |                  | [    |     | 0.5             | V    |

| Internal Pull-Up Resistor                       |                |                  | }    |     | 15              | kΩ   |

| Buffers                                         | 1 to 6,        |                  |      |     |                 |      |

| Mean Value of min. and max. Buffer Currents     | 8 to 15,       | l <sub>BB</sub>  | 9    | 11  | 13              | mA   |

| $(V_{CO} = V_{CC}, V_{LE} = 0)$                 | 23, 24         |                  |      |     |                 |      |

| Buffer Current Variation around IBB             |                |                  | -7%  |     | +7%             |      |

| Saturation Voltage                              |                | v <sub>s</sub>   |      | 1.2 | 1.8             | v    |

| Output Impedance                                |                | rout             |      | 100 |                 | kΩ   |

| Leakage Current (VBB=5V)                        |                | l <sub>B</sub> L | }    |     | 10              | μА   |

| Supply Current LED-Test (V <sub>LE</sub> = 5V)  | 18             | 1 <sub>LE</sub>  | 3    | 4.3 | 6               | mA   |

| Supply Current                                  | 17             | 1cc              | 18   | [   | 50              | mA   |

| Power Dissipation, all Buffers ON               |                |                  | 1    | 650 |                 | mW   |

| $(V_{CO} = V_{LE} = V_{CC})$ at $V_{BB} = 2.9V$ |                |                  |      |     |                 |      |

| Ambient Temperature                             |                | TA               | 0    |     | 70              | °c   |

| Package Thermal Resistance                      |                | R <sub>th</sub>  |      | 70  |                 | °C/W |

All Voltages referenced to ground (Pin 7)

1) Brightness goes to zero at 2V

### MAXIMUM RATINGS (TA= 25°C)

| Rating                                                             | Pin                       | Symbol           | Value       | Unit |

|--------------------------------------------------------------------|---------------------------|------------------|-------------|------|

| Logic Input Voltages                                               | 19, 20, 21                | V <sub>LOG</sub> | 10          | ٧    |

| Con trol Vol tage                                                  | 16                        | v <sub>co</sub>  | 10          | V    |

| Supply Voltage                                                     | 17                        | v <sub>cc</sub>  | 10          | V    |

| Control Voltage                                                    | 18                        | VLE              | 10          | ٧    |

| Data-Out, max. Voltage (ID = 2mA)                                  | 22                        | v <sub>D</sub>   | 10          | v    |

| Buffers Output Voltage $\{V_{CC} = V_{CO} = 5.5V\}$ All Buffers ON | 1 to6<br>8to 15<br>23, 24 | V <sub>88</sub>  | 6           | v    |

| Storage Temperature                                                |                           | <sup>T</sup> STG | -50 to +150 | °c   |

| Operating Ambient Temperature                                      |                           | TA               | 0 to 70     | °C-  |

All voltages referenced to ground (Pin 7)

### SWITCHING CHARACTERISTICS (TA= 0 to $70^{\circ}$ C, see figure 3 )

| Characteristic                                | Symbol                                 | Min | Max | Unit |

|-----------------------------------------------|----------------------------------------|-----|-----|------|

| Clock "High"-Time                             | ,CH                                    | 3   | ]   | μs   |

| Clock "Low"-Time                              | 'CL                                    | 3   |     | μş   |

| Negative going VDR Edge to first Clock Edae   | †LVC                                   | 10  |     | μs   |

| Last Clock Edge to positive going VDR Edge    | <sup>t</sup> LCV                       | 1   |     | μς   |

| Data Change to positive going Clock Edge      | †LDC                                   | 1   |     | μs   |

| Positive going Clock Edge to Data Change      | †LCD                                   | 3   |     | μs   |

| Rise Times of Digital Inputs VDR, Clock, Data | tRV+ TRC+ TRD                          |     | 2   | μs   |

| Fall Timet of Digital Inputs VDR, Clock, Data | t <sub>EV</sub> ,t <sub>EC</sub> , 'FD |     | 2   | μS   |