|

ąÜą░ąČą┤ą░čÅ čüąĖčüč鹥ą╝ą░ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ą”ąÉą¤, ą░ąĮą│ą╗ąĖą╣čüą║ą░čÅ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ DAC) ąĮą░ ąŠčüąĮąŠą▓ąĄ čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ ą╝ąŠą┤čāą╗čÅčåąĖąĖ (ą©ąśą£, PWM) ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, čćč鹊ą▒čŗ ąŠčéą┤ąĄą╗ąĖčéčī čüą┐ąĄą║čéčĆ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£ ąŠčé čüą┐ąĄą║čéčĆą░ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąĪą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ čéą░ą║ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ - ążąØą¦ ąĮą░ ąŠčüąĮąŠą▓ąĄ RC-čåąĄą┐ąŠčćą║ąĖ, čā ą║ąŠč鹊čĆąŠą│ąŠ čĆą░ąĘą╝ą░čģ ą┐čāą╗čīčüą░čåąĖą╣ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£ (ą┤ą╗čÅ čüą░ą╝ąŠą│ąŠ ą┐ą╗ąŠčģąŠą│ąŠ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ čüą║ą▓ą░ąČąĮąŠčüčéčī ą©ąśą£ čüąŠčüčéą░ą▓ą╗čÅąĄčé 50%), čüąŠčüčéą░ą▓ąĖčé (ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ RC ą▒ąŠą╗čīčłąĄ ą┐ąĄčĆąĖąŠą┤ą░ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£ TPWM):

Vripple / Vfullscale = TPWM / 4┬ĘRC

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čüčéą░čéčīąĖ Stephen Woodward [1] čü ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąĖąĘ čüčéą░čéčīąĖ [3].

ą×č湥ą▓ąĖą┤ąĮčŗą╣ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčü ą▓ čŹč鹊ą╝ čüą┐ąŠčüąŠą▒ąĄ ą▒ąŠčĆčīą▒čŗ čü ą┐čāą╗čīčüą░čåąĖčÅą╝ąĖ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ č鹊ą╝, čćč鹊 čģąŠčéčÅ ą╗čÄą▒ą░čÅ čüč鹥ą┐ąĄąĮčī ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖčÅ ą┐čāą╗čīčüą░čåąĖą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮą░ ą┐čāč鹥ą╝ ą▓čŗą▒ąŠčĆą░ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒ąŠą╗čīčłąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ RC, ą┐čĆąĖ čŹč鹊ą╝ ą┐ąŠčüčéčĆą░ą┤ą░ąĄčé čüą║ąŠčĆąŠčüčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ, čé. ąĄ. ą▓ą╝ąĄčüč鹥 čü ąĖą╝ą┐čāą╗čīčüą░ą╝ąĖ ą©ąśą£ ą▒čāą┤ąĄčé ą▓čŗčĆąĄąĘą░ąĮą░ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮą░čÅ čüąŠčüčéą░ą▓ą╗čÅčÄčēą░čÅ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ą╝čŗ ą▓čŗą▒ąĖčĆą░ąĄą╝ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą┐ąŠą╗ąŠčüčŗ čüčĆąĄąĘą░ čäąĖą╗čīčéčĆą░ ą┐ąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╝čā čāčĆąŠą▓ąĮčÄ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐čāą╗čīčüą░čåąĖą╣, čĆą░ą▓ąĮąŠą╝čā ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĄ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (čćč鹊 ą┤ąŠą▓ąŠą╗čīąĮąŠ ą╗ąŠą│ąĖčćąĮąŠ), č鹊 ą▓čĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ Tsettle čüąŠčüčéą░ą▓ąĖčé (ąĘą┤ąĄčüčī Vfullscale čŹč鹊 ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░ ą▓čģąŠą┤ąĄ čäąĖą╗čīčéčĆą░, Vripple ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ ą┐čāą╗čīčüą░čåąĖą╣ ąĮą░ ą▓čŗčģąŠą┤ąĄ čäąĖą╗čīčéčĆą░):

Tsettle = RC┬Ęln(Vfullscale / Vripple) = TPWM ┬Ę Vfullscale ┬Ęln(Vfullscale / Vripple) / (4┬ĘVripple)

ąŁčéčā ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą╝ąŠąČąĮąŠ ą┐čĆąŠą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆąŠą▓ą░čéčī ąĮą░ ą┐čĆąĖą╝ąĄčĆąĄ 8-ą▒ąĖčéąĮąŠą│ąŠ ą©ąśą£. ąĢčüą╗ąĖ ą▓ąĘčÅčéčī:

Vripple / Vfullscale = 1/256; RC = 64┬ĘTPWM

... č鹊 ą┐ąŠą╗čāčćąĖčéčüčÅ:

Tsettle = 64┬Ęln(256)┬ĘTPWM = 355┬ĘTPWM

ą¤ąŠą╗čāčćą░ąĄčéčüčÅ, čćč鹊 ą┤ą░ąČąĄ ą┤ą╗čÅ ą┤ąŠą▓ąŠą╗čīąĮąŠ ą▒čŗčüčéčĆąŠą│ąŠ ą©ąśą£ 32 ą║ąōčå (TPWM = 31 ą╝ą║čü) ą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠąĄ ą▓čĆąĄą╝čÅ ąĘą░ą┐ą░ąĘą┤čŗą▓ą░ąĮąĖčÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ čüąŠčüčéą░ą▓ąĖčé 11 ą╝čü (čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąŠą╗ąĄąĘąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā 90 ąōčå).

ą×č湥ą▓ąĖą┤ąĮąŠ, čćč鹊 ąĄčüą╗ąĖ ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čÅą▓ą╗čÅąĄčéčüčÅ ą║čĆąĖčéąĖč湥čüą║ąĖą╝ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą╝ ą┤ą╗čÅ ą”ąÉą¤, č鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čćč鹊-č鹊 čāą╗čāčćčłąĖčéčī ą▓ čüčģąĄą╝ąĄ ąĖ/ąĖą╗ąĖ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą▒ąŠą╗ąĄąĄ čüą╗ąŠąČąĮčāčÄ čüčģąĄą╝čā čäąĖą╗čīčéčĆą░čåąĖąĖ. ą×ą┤ąĖąĮ ąĖąĘ čéą░ą║ąĖčģ ą┐ąŠą┤ąŠą▒ąĮčŗčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čäąĖą╗čīčéčĆą░ ą┐ąŠą║ą░ąĘą░ąĮ ą▓ čüčéą░čéčīąĄ [2].

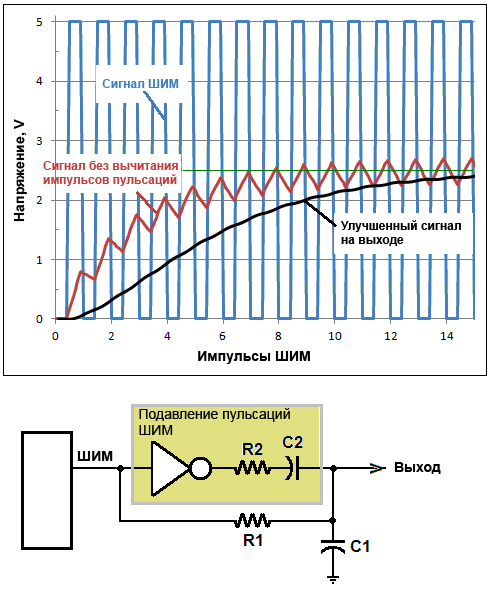

ą×ą┤ąĮą░ą║ąŠ ąĮąĄ ą▓ ą║ą░ąČą┤ąŠą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ą┤ąŠą┐čāčüčéąĖą╝ąŠ ą┐čĆąĖą╝ąĄąĮčÅčéčī čéą░ą║ąŠąĄ čüą╗ąŠąČąĮąŠąĄ čĆąĄčłąĄąĮąĖąĄ. ąśą┤ąĄčÅ čĆąĄčłąĄąĮąĖčÅ, ą┐čĆąĄą┤ą╗ą░ą│ą░ąĄą╝ąŠąĄ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ, ą║ą░čüą░ąĄčéčüčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čüčĆąĄą┤ąĮąĄą│ąŠ ą║ą╗ą░čüčüą░. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 1, čĆąĄčłąĄąĮąĖąĄ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ą║ ą▒ą░ąĘąŠą▓ąŠą╝čā ążąØą¦ ąĮą░ R1C1 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ąĖąĮą▓ąĄčĆč鹊čĆ ąĖ 菹╗ąĄą╝ąĄąĮčéčŗ R2 ąĖ C2, ą║ąŠč鹊čĆčŗąĄ čüą╝ąĄčłąĖą▓ą░čÄčé čü ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╝ ąĘąĮą░ą║ąŠą╝ ą┐ąŠą╗ąĄąĘąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĖ ąĖą╝ą┐čāą╗čīčüčŗ ą┐čāą╗čīčüą░čåąĖą╣. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čćąĖčüčéčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠą╗ąĄąĘąĮčŗą╣ čüąĖą│ąĮą░ą╗, ą║ąŠč鹊čĆčŗą╣ ąĮą░ą╝ąĮąŠą│ąŠ ą╗čāčćčłąĄ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą╗čāčćąĖą╗čüčÅ ą▒čŗ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┐čĆąŠčüč鹊ą│ąŠ RC-čäąĖą╗čīčéčĆą░.

ąĀąĖčü. 1. ążąŠčĆą╝čŗ čüąĖą│ąĮą░ą╗ą░ ąĖ čüčģąĄą╝ą░ ą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čÅ ą┐čāą╗čīčüą░čåąĖą╣ ą©ąśą£.

ą×ą┤ąĮą░ą║ąŠ ąĮą░čüą║ąŠą╗čīą║ąŠ čćąĖčüčéčŗą╣ ą┐ąŠą╗čāčćąĖčéčüčÅ čŹč鹊čé "ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čćąĖčüčéčŗą╣ čüąĖą│ąĮą░ą╗", ąĖ ąĮą░čüą║ąŠą╗čīą║ąŠ ą▒čŗčüčéčĆąĄąĄ ą┐ąŠą╗čāčćąĖčéčüčÅ ąĮą░čĆą░čüčéą░ąĮąĖąĄ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ? ąĢčüą╗ąĖ ą┐čĆąĖąĮčÅčéčī R2=R1, ąĖ R2=C1, č鹊 čāčĆąŠą▓ąĄąĮčī ą┐čāą╗čīčüą░čåąĖą╣ ąĖ ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓ ąĮąŠą▓ąŠą╣ čüčģąĄą╝ąĄ ą┐ąŠą╗čāčćą░čéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ:

Vripple / Vfullscale = (TPWM / 4┬ĘRC)2

Tsettle = TPWM ┬Ęln(Vfullscale / Vripple )┬Ę(Vfullscale / 16┬ĘVripple )1/2

ąś ą┤ą╗čÅ čüą╗čāčćą░čÅ 8-ą▒ąĖčéąĮąŠą│ąŠ ą©ąśą£ (čüąĖą│ąĮą░ą╗čŗ ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 1) ą┐ąŠą╗čāčćąĖčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąĖąĮčÅčéčī RC = 4┬ĘTPWM:

Tsettle = 22┬ĘTPWM = 0.69 ą╝čü

ąØą░ čćą░čüč鹊č鹥 ą©ąśą£ 32 ą║ąōčå čŹčéą░ čüčģąĄą╝ą░ čĆą░ą▒ąŠčéą░ąĄčé ą▓ 16 čĆą░ąĘ ą▒čŗčüčéčĆąĄąĄ. ąöą╗čÅ ą╝ąĮąŠą│ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čŹč鹊 ą╝ąŠąČąĄčé ąŠą║ą░ąĘą░čéčīčüčÅ ąŠč湥ąĮčī čģąŠčĆąŠčłąĖą╝ ą▓ą░čĆąĖą░ąĮč鹊ą╝ ą┤ą╗čÅ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčüą░ ą╝ąĄąČą┤čā čüą╗ąŠąČąĮąŠčüčéčīčÄ čüčģąĄą╝čŗ ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ą©ąśą£ ą┤ą╗čÅ ą”ąÉą¤.

[ąŻą╗čāčćčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čüčģąĄą╝čŗ]

ą×čüąĮąŠą▓ąĮąŠą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ ą┐ąŠą║ą░ąĘą░ąĮąĮąŠą╣ ą▓čŗčłąĄ čüčģąĄą╝čŗ - ą┐ą░čüčüąĖą▓ąĮąŠąĄ čüčāą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ (čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄąĘąĖčüč鹊čĆąŠą▓ R1 ąĖ R2) ąŠčüąĮąŠą▓ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£ ąĖ ąĖąĮą▓ąĄčĆčüąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£ (ą┐čĆąŠčģąŠą┤čÅčēąĄą│ąŠ č湥čĆąĄąĘ C2) čü ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ čāčüčĆąĄą┤ąĮąĄąĮąĖąĄą╝ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąĄ C1. ąĀąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĄąĄ čćą░čüčéąĖčćąĮąŠąĄ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖą╝ąĄąĮąĖčéčī ą╝ąĄąĮčīčłčāčÄ ą┐ąŠčüč鹊čÅąĮąĮčāčÄ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čäąĖą╗čīčéčĆą░.

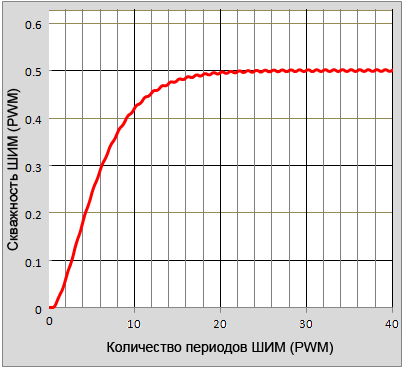

ą×ą┤ąĮą░ą║ąŠ ąĮąĄą┤ąŠčüčéą░č鹊ą║ čéą░ą║ąŠą╣ čüčģąĄą╝čŗ čüčāą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ č鹊ą║ąŠą▓, ą║ąŠč鹊čĆčŗą╣ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčé čüą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ, čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čüčéčāą┐ąĄąĮčćą░č鹊ą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ PWM č鹊ą║ąĖ R1 ąĖ R2 ą▒čāą┤čāčé ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╝ąĖ ą┐ąŠ ąĘąĮą░ą║čā, ąĮąŠ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ąĖ ą┐ąŠ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĄ, čéą░ą║ čćč鹊 ąĖčģ ą╝ą│ąĮąŠą▓ąĄąĮąĮą░čÅ čüčāą╝ą╝ą░ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ąŠą║ą░ąČąĄčéčüčÅ čĆą░ą▓ąĮąŠą╣ 0. ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ, ąĮą░ C1 ąĮąĄč湥ą╝čā ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░čéčīčüčÅ, ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ DAC ąĮąĄ ą╝ąŠąČąĄčé ąĮą░čćą░čéčī čĆąĄą░ą│ąĖčĆąŠą▓ą░čéčī ąĮą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čłą░ą│ą░, ą┐ąŠą║ą░ C2 ąĮąĄ ąĮą░čćąĮąĄčé ąĘą░čĆčÅąČą░čéčīcčÅ, čāą╝ąĄąĮčīčłą░čÅ č鹊ą║ č湥čĆąĄąĘ R2, ą┤ąĄą╗ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ č鹊ą║ąĖ R1 ąĖ R2 ąĮąĄąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ąĖ, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ąĮą░ C1 ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčÅą▓ąĖčéčīčüčÅ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗. ąŁč鹊čé ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗą╣ ąĮčāą╗ąĄą▓ąŠą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 2 ą║ą░ą║ ą▓čĆąĄą╝ąĄąĮąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░, ą║ąŠč鹊čĆą░čÅ ą▓ąĖą┤ąĮą░ ąĮą░ ą┐ąĄčĆąĄą┤ąĮąĄą╝ čäčĆąŠąĮč鹥 ąĮą░čĆą░čüčéą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 2. ą×čéą▓ąĄčé ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčćąĖčéą░ąĮąĖąĄ č鹊ą║ąŠą▓ ą┐čāą╗čīčüą░čåąĖą╣.

ąŁč鹊 ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ ąŠčéą║ą╗ąĖą║ą░ ą▓čŗčģąŠą┤ą░ DAC ą▓ąĄčĆąŠčÅčéąĮąŠ ą┐čĆąĄąŠą┤ąŠą╗ąĄčéčī ąĮąĄ ą┐ąŠą╗čāčćąĖčéčüčÅ ąĖąĘ-ąĘą░ ą┐čĆąĖą╝ąĄąĮčÅąĄą╝ąŠą╣ č鹊ą┐ąŠą╗ąŠą│ąĖąĖ čüčāą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ č鹊ą║ąŠą▓ ąĮą░ čĆąĄąĘąĖčüč鹊čĆą░čģ. ąźąŠčéčÅ čŹčéą░ čüčģąĄą╝ą░ čäąĖą╗čīčéčĆą░ ą▓čüąĄ ąĄčēąĄ ąĮą░ą╝ąĮąŠą│ąŠ čŹčäč乥ą║čéąĖą▓ąĮąĄąĄ, č湥ą╝ ąŠą▒čŗčćąĮčŗą╣ ą┐čĆąŠčüč鹊ą╣ RC-čäąĖą╗čīčéčĆ, ąŠą┤ąĮą░ą║ąŠ ąŠąĮą░ ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆą░čÅ, ą║ą░ą║ ąŠąĮą░ ą╝ąŠą│ą╗ą░ (ą┤ąŠą╗ąČąĮą░) ą▒čŗ ą▒čŗčéčī.

ą¦č鹊 ą╝ąŠą│ą╗ąŠ ą▒čŗ ą┐ąŠą╗čāčćąĖčéčīčüčÅ, ąĄčüą╗ąĖ ą▓ą╝ąĄčüč鹊 ą┐čĆąŠčüč鹊ą│ąŠ ą▓čŗčćąĖčéą░ąĮąĖčÅ č鹊ą║ąŠą▓ čüąĮą░čćą░ą╗ą░ ą▓čŗčćąĖčüą╗čÅą╗ąĖčüčī ą▒čŗ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą©ąśą£ ąĖ ą┐čāą╗čīčüą░čåąĖą╣, ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąŠąĮąĖ ą▓čŗčćąĖčéą░ą╗ąĖčüčī ą▒čŗ, čćč鹊ą▒čŗ ą┐čĆąŠąĖčüčģąŠą┤ąĖą╗ąŠ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ ą┐čāą╗čīčüą░čåąĖą╣? ą£ąŠąČąĮąŠ ą╗ąĖ čćč鹊-ąĮąĖą▒čāą┤čī ąĄčēąĄ ą▓čŗąČą░čéčī ąĖąĘ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą╣ ąĖą┤ąĄąĖ, čćč鹊ą▒čŗ ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ ą┐čĆąŠčüč鹊čéčŗ ąŠąĮą░ čĆą░ą▒ąŠčéą░ą╗ą░ ą▒čŗ ą▒ąŠą╗ąĄąĄ čŹčäč乥ą║čéąĖą▓ąĮąŠ? ą×čéą▓ąĄč鹊ą╝ ąĮą░ čŹčéąĖ ą▓ąŠą┐čĆąŠčüčŗ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 čĆą░čüč湥č鹊ą▓ ąĖ 菹║čüą┐ąĄčĆąĖą╝ąĄąĮč鹊ą▓ ą┐ąŠčÅą▓ąĖą╗ą░čüčī čüą╗ąĄą┤čāčÄčēą░čÅ čüčģąĄą╝ą░.

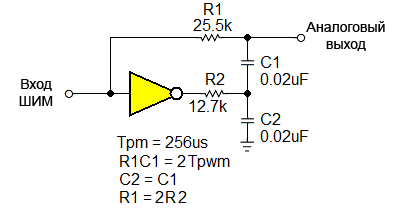

ąĀąĖčü. 3. ąØąŠą▓ą░čÅ čüčģąĄą╝ą░ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą┐čāą╗čīčüą░čåąĖą╣ čü ą▓čŗčćąĖčéą░ąĮąĖąĄą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣.

ąĀą░ą▒ąŠčéą░ ąĮąŠą▓ąŠą╣ čüčģąĄą╝čŗ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╝ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ C1 (ą║ąŠč鹊čĆčŗą╣ čüąŠąĘą┤ą░ąĄčé ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčā ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ PWM) ąĖ C2 (ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐čāą╗čīčüą░čåąĖą╣). ą×ą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ, čćč鹊 ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ ą┐čāą╗čīčüą░čåąĖą╣, ą░ą┤ąĄą║ą▓ą░čéąĮąŠąĄ 8-ą▒ąĖčéąĮąŠą╣ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ R1C1 čĆą░ą▓ąĮą░ 2Tpwm, čé. ąĄ. čāą┤ą▓ąŠąĄąĮąĮąŠą╝čā ą┐ąĄčĆąĖąŠą┤čā PWM. ąØą░ą┐čĆąĖą╝ąĄčĆ, 512 ą╝ą║čü ą┤ą╗čÅ 8-ą▒ąĖčéąĮąŠą╣ PWM, čüč湥čéčćąĖą║ ą║ąŠč鹊čĆąŠą╣ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 1 ą£ąōčå (ą┐ąĄčĆąĖąŠą┤ ą©ąśą£ = 256 / 1000000 = 256 ą╝ą║čü). ą¤čĆąĖ čāą▓ąĄą╗ąĖč湥ąĮąĖąĖ čćą░čüč鹊čéčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ čāą╝ąĄąĮčīčłą░čÄčéčüčÅ ąĖ ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĮąĄ čāą▓ąĄą╗ąĖčćąĖą╗ąŠčüčī - ąŠčüčéą░ą╗čüčÅ ąŠą┤ąĖąĮ ąĖąĮą▓ąĄčĆč鹥čĆ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, 1/6 ą║ąŠčĆą┐čāčüą░ SN74HC04), 2 čĆąĄąĘąĖčüč鹊čĆą░ ąĖ 2 ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░.

ąĀąĖčü. 4 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčéčāą┐ąĄąĮčćą░čéčŗą╣ ąŠčéą▓ąĄčé ąĮą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéąĖ PWM, ą║ąŠč鹊čĆčŗą╣ č鹥ą┐ąĄčĆčī čüčĆą░ąĘčā ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé T = 0, ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąĘą░ą┤ąĄčƹȹ║ąĖ, ą┐ąŠą║ą░ąĘą░ąĮąĮąŠą╣ ąĮą░ čĆąĖčü. 2, ą║ąŠą│ą┤ą░ ą┐čĆąĖą╝ąĄąĮčÅą╗čüčÅ č鹊ą║ąŠą▓čŗą╣ ą┐čĆąĖąĮčåąĖą┐ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą┐čāą╗čīčüą░čåąĖą╣.

ąĀąĖčü. 4. ąĀą░ą▒ąŠčéą░ čüčģąĄą╝čŗ, ąŠčüąĮąŠą▓ą░ąĮąĮą░čÅ ąĮą░ ą▓čŗčćąĖčéą░ąĮąĖąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣.

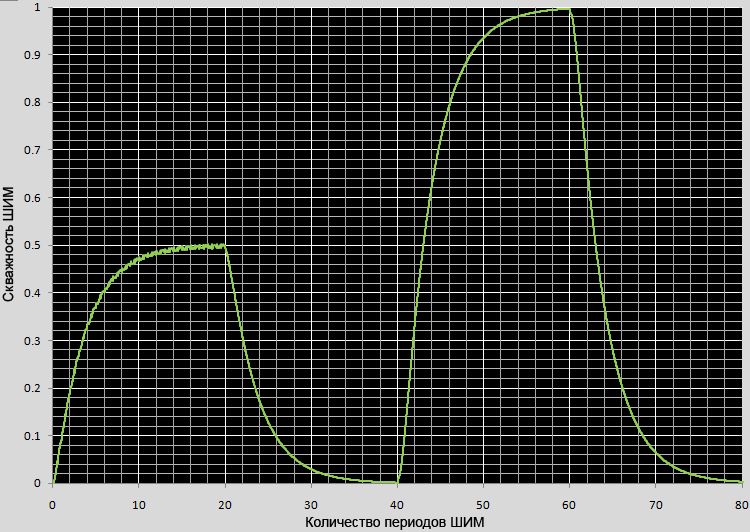

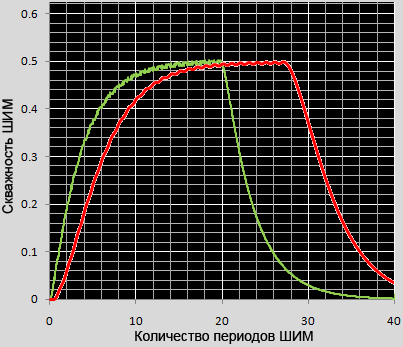

ąØą░ čĆąĖčü. 5 ą┐ąŠą║ą░ąĘą░ąĮąŠ čüčĆą░ą▓ąĮąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čüčéą░čĆąŠą╣ (ą║čĆą░čüąĮčŗą╣ ą│čĆą░čäąĖą║) ąĖ ąĮąŠą▓ąŠą╣ čüčģąĄą╝čŗ (ąĘąĄą╗ąĄąĮčŗą╣ ą│čĆą░čäąĖą║). ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąŠčéą║ą╗ąĖą║ą░ čā čüčéą░čĆąŠą╣ čüčģąĄą╝čŗ ~23 ą┐ąĄčĆąĖąŠą┤ą░ PWM, ą░ čā ąĮąŠą▓ąŠą╣ čüčģąĄą╝čŗ ~16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ PWM. ąŻą▓ąĄą╗ąĖč湥ąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ ąŠčéą║ą╗ąĖą║ą░ ąĮą░ 44% ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ ąŠč湥ąĮčī ą┐ąŠą╗ąĄąĘąĮčŗą╝, ąĄčüą╗ąĖ čāč湥čüčéčī, čćč鹊 čüčģąĄą╝ą░ ąĮąĄ čāčüą╗ąŠąČąĮąĖą╗ą░čüčī ąĖ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĮąĄ čāą▓ąĄą╗ąĖčćąĖą╗ąŠčüčī.

ąĀąĖčü. 5. ąĪčĆą░ą▓ąĮąĄąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ čĆą░ą▒ąŠčéčŗ čüčéą░čĆąŠą╣ ąĖ ąĮąŠą▓ąŠą╣ čüčģąĄą╝čŗ.

[ąĪčüčŗą╗ą║ąĖ]

1. Cancel PWM DAC ripple with analog subtraction site:edn.com.

2. ąæčŗčüčéčĆčŗą╣ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čäąĖą╗čīčéčĆ ą┤ą╗čÅ ą”ąÉą¤ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą©ąśą£.

3. Cancel PWM DAC ripple with analog subtraction revisited site:ednasia.com.

4. ąæčŗčüčéčĆčŗą╣ PWM DAC ą▒ąĄąĘ ą▓čŗčģąŠą┤ąĮčŗčģ ą┐čāą╗čīčüą░čåąĖą╣.

5. Phased-array PWM DAC site:edn.com.

6. Cancel PWM DAC ripple with analog subtraction but no inverter site:edn.com. |